**LECTURE NOTES ON**

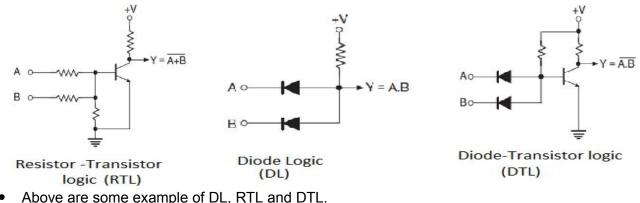

# **DIGITAL ELECTRONICS**

SEM-3<sup>RD</sup>

**Prepared By**

Er. Sabyasachi Patra

Asst.Prof. Electronics & Tele-Communication Engineering

Department of Electronics & Tele-Communication Engineering

C V RAMAN POLYTECHNIC

**BBSR**

# NUMBER SYSTEM AND CODES

# **INTRODUCTION:-**

- The term digital refers to a process that is achieved by using discrete unit.

- In number system there are different symbols and each symbol has an absolute value and also has place value.

# **RADIX OR BASE:-**

The radix or base of a number system is defined as the number of different digits which can occur in each position in the number system.

# **RADIX POINT :-**

The generalized form of a decimal point is known as radix point. In any positional number system the radix point divides the integer and fractional part.

N<sub>r</sub> = [Integer part Fractional part]

Radix point

# NUMBER SYSTEM:-

In general a number in a system having base or radix 'r' can be written as

$a_n \quad a_{n-1} \quad a_{n-2} \quad \dots \quad a_0 \quad a_{-1} \quad a_{-2} \quad \dots \quad a_{-m}$

This will be interpreted as

$Y = a_n x r^n + a_{n-1} x r^{n-1} + a_{n-2} x r^{n-2} + \dots + a_0 x r^0 + a_{-1} x r^{-1} + a_{-2} x r^{-2} + \dots + a_{-m} x r^{-m}$

where Y = value of the entire number

$a_n$  = the value of the n<sup>th</sup> digit

r = radix

# **TYPES OF NUMBER SYSTEM:-**

There are four types of number systems. They are

- 1. Decimal number system

- 2. Binary number system

- 3. Octal number system

- 4. Hexadecimal number system

# **DECIMAL NUMBER SYSTEM:-**

- The decimal number system contain ten unique symbols 0,1,2,3,4,5,6,7,8 and 9.

- In decimal system 10 symbols are involved, so the base or radix is 10.

- It is a positional weighted system.

- The value attached to the symbol depends on its location with respect to the decimal point.

In general,

$$d_n \ d_{n\text{-}1} \ d_{n\text{-}2} \ \ldots \ d_0 \ . \ d_{\text{-}1} \ d_{\text{-}2} \ \ldots \ \ldots \ d_{\text{-}m}$$

is given by

$$(d_n \times 10^n) + (d_{n-1} \times 10^{n-1}) + (d_{n-2} \times 10^{n-2}) + ... + (d_0 \times 10^0) + (d_{-1} \times 10^{-1}) + (d_{-2} \times 10^{-2}) + ... + (d_{-m} \times 10^{-m})$$

### For example:-

$9256.26 = 9 \times 1000 + 2 \times 100 + 5 \times 10 + 6 \times 1 + 2 \times (1/10) + 6 \times (1/100)$

$= 9 \times 10^{3} + 2 \times 10^{2} + 5 \times 10^{1} + 6 \times 10^{0} + 2 \times 10^{-1} + 6 \times 10^{-2}$

# **BINARY NUMBER SYSTEM:-**

- The binary number system is a positional weighted system.

- The base or radix of this number system is 2.

- It has two independent symbols.

- The symbols used are 0 and 1.

- A binary digit is called a bit.

- The binary point separates the integer and fraction parts.

In general,

$d_n \quad d_{n-1} \quad d_{n-2} \quad \dots \quad d_0 \quad d_{-1} \quad d_{-2} \quad \dots \quad d_{-k}$

is given by

$(d_n \times 2^n) + (d_{n-1} \times 2^{n-1}) + (d_{n-2} \times 2^{n-2}) + \dots + (d_0 \times 2^0) + (d_{-1} \times 2^{-1}) + (d_{-2} \times 2^{-2}) + \dots + (d_{-k} \times 2^{-k})$

# **OCTAL NUMBER SYSTEM:-**

- It is also a positional weighted system.

- Its base or radix is 8.

- It has 8 independent symbols 0,1,2,3,4,5,6 and 7.

- Its base  $8 = 2^3$ , every 3- bit group of binary can be represented by an octal digit.

# HEXADECIMAL NUMBER SYSTEM:-

- The hexadecimal number system is a positional weighted system.

- The base or radix of this number system is 16.

- The symbols used are 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E and F

- The base 16 = 24, every 4 bit group of binary can be represented by an hexadecimal digit.

# **CONVERSION FROM ONE NUMBER SYSTEM TO ANOTHER** :-

# 1. <u>BINARY NUMBER SYSTEM</u>:-

(a) Binary to decimal conversion:-

In this method, each binary digit of the number is multiplied by its positional weight and the product terms are added to obtain decimal number.

#### For example:

### (i) Convert $(10101)_2$ to decimal.

# Solution :

(Positional weight)  $2^4 2^3 2^2 2^1 2^0$ Binary number 10101 $= (1 \times 2^4) + (0 \times 2^3) + (1 \times 2^2) + (0 \times 2^1) + (1 \times 2^0)$ = 16 + 0 + 4 + 0 + 1 $= (21)_{10}$

### (ii) Convert $(111.101)_2$ to decimal.

## Solution:

$$(111.101)_2 = (1 \times 2^2) + (1 \times 2^1) + (1 \times 2^0) + (1 \times 2^{-1}) + (0 \times 2^{-2}) + (1 \times 2^{-3})$$

= 4+2+1+0.5+0+0.125

= (7.625)\_{10}

# (b)Binary to Octal conversion:-

For conversion binary to octal the binary numbers are divided into groups of 3 bits each, starting at the binary point and proceeding towards left and right.

| <u>Octal</u> | Binary | <u>Octal</u> | <u>Binary</u> |

|--------------|--------|--------------|---------------|

| 0            | 000    | 4            | 100           |

| 1            | 001    | 5            | 101           |

| 2            | 010    | 6            | 110           |

| 3            | 011    | 7            | 111           |

For example:

# (i) Convert (101111010110.110110011)<sub>2</sub> into octal.

# Solution :

| Group of 3 bits are                          | 101 | 111 | 010 | 110 |  | 110 | 110 | 011 |

|----------------------------------------------|-----|-----|-----|-----|--|-----|-----|-----|

| Convert each group into octal =              | 5   | 7   | 2   | 6   |  | 6   | 6   | 3   |

| The result is <b>(5726.663)</b> <sub>8</sub> |     |     |     |     |  |     |     |     |

| (ii) Convert (10101111001.0111)₂ into octal. |     |     |     |     |  |     |     |     |

| Solution :<br>Binary number                  | 10  | 101 | 111 | 001 |  | 011 | 1   |     |

| Group of 3 bits are =                        | 010 | 101 | 111 | 001 |  | 011 | 100 |     |

| Convert each group into octal =              | 2   | 5   | 7   | 1   |  | 3   | 4   |     |

| The result is (2571.34) <sub>8</sub>         |     |     |     |     |  |     |     |     |

# (c) Binary to Hexadecimal conversion:-

For conversion binary to hexadecimal number the binary numbers starting from the binary point, groups are made of 4 bits each, on either side of the binary point.

| <u>Hexadecimal</u> | Binary | <u>Hexadecimal</u> | <b>Binary</b> |

|--------------------|--------|--------------------|---------------|

| 0                  | 0000   | 8                  | 1000          |

| 1                  | 0001   | 9                  | 1001          |

| 2                  | 0010   | A                  | 1010          |

| 3                  | 0011   | В                  | 1011          |

| 4                  | 0100   | С                  | 1100          |

| 5                  | 0101   | D                  | 1101          |

| 6                  | 0110   | E                  | 1110          |

| 7                  | 0111   | F                  | 1111          |

### For example:

(i) Convert (1011011011)<sub>2</sub> into hexadecimal.

#### Solution:

| Given Binary number            |   | 10   | 1101 | 1011 |  |

|--------------------------------|---|------|------|------|--|

| Group of 4 bits are            |   | 0010 | 1101 | 1011 |  |

| Convert each group into hex    | = | 2    | D    | В    |  |

| The result is ( <b>2DB)</b> 16 |   |      |      |      |  |

### (ii) Convert $(01011111011.011111)_2$ into hexadecimal.

#### Solution:

| Given Binary number             | 010  | 1111 | 1011 | • | 0111 | 11   |

|---------------------------------|------|------|------|---|------|------|

| Group of 3 bits are =           | 0010 | 1111 | 1011 |   | 0111 | 1100 |

| Convert each group into octal = | 2    | F    | В    |   | 7    | С    |

The result is (2FB.7C)<sub>16</sub>

# 2. <u>DECIMAL NUMBER SYSTEM</u>:-

### (a)Decimal to binary conversion:-

In the conversion the integer number are converted to the desired base using successive division by the base or radix.

### For example:

#### (i) Convert $(52)_{10}$ into binary.

#### Solution:

Divide the given decimal number successively by 2 read the integer part remainder upwards to get equivalent binary number. Multiply the fraction part by 2. Keep the integer in the product as it is and multiply the new fraction in the product by 2. The process is continued and the integer are read in the products from top to bottom.

| 2 <u>  52</u> |     |

|---------------|-----|

| 2 <u>  26</u> | — 0 |

| 2 <u>  13</u> | — 0 |

| 2 <u> 6</u>   | — 1 |

| 2 <u> 3</u>   | — 0 |

| 2 <u> 1</u>   | — 1 |

| 0             | — 1 |

### Result of (52)<sub>10</sub> is (110100)<sub>2</sub>

(ii) Convert (105.15)<sub>10</sub> into binary.

### Solution:

| Integer part        | Fraction part   |

|---------------------|-----------------|

| 2 <u>  105  </u>    | 0.15 x 2 = 0.30 |

| 2 <u> 52</u> — 1    | 0.30 x 2 = 0.60 |

| 2 <u> 26</u> — 0    | 0.60 x 2 = 1.20 |

| 2 <u> 13</u> — 0    | 0.20 x 2 = 0.40 |

| 2 <u> 6</u> — 1     | 0.40 x 2 = 0.80 |

| 2 <u> 3</u> — 0     | 0.80 x 2 = 1.60 |

| 2 <u> 1</u> — 1     |                 |

| 0 — 1               |                 |

| in (1101001 001001) |                 |

Result of  $(105.15)_{10}$  is  $(1101001.001001)_2$

# (b)Decimal to octal conversion:-

To convert the given decimal integer number to octal, successively divide the given number by 8 till the quotient is 0. To convert the given decimal fractions to octal successively multiply the decimal fraction and the subsequent decimal fractions by 8 till the product is 0 or till the required accuracy is obtained.

#### For example: (i) Convert (378.93)<sub>10</sub> into octal.

### Solution:

| 8 <u>  378</u> |     | 0.93 x 8 = 7.44 |

|----------------|-----|-----------------|

| 8 <u>  47</u>  | — 2 | 0.44 x 8 = 3.52 |

| 8 <u> 5</u>    | — 7 | 0.52 x 8 = 4.16 |

| 0              | — 5 | 0.16 x 8 = 1.28 |

Result of (378.93)10 is (572.7341)8

# (c)Decimal to hexadecimal conversion:-

The decimal to hexadecimal conversion is same as octal.

### For example:

(i) Convert (2598.675)<sub>10</sub> into hexadecimal.

### Solution:

| Remain<br>Decimal   |   |                   | Hex |

|---------------------|---|-------------------|-----|

| 16 <u>  2598</u>    |   | 0.675 x 16 = 10.8 | А   |

| 16 <u>  162</u> — 6 | 6 | 0.800 x 16 = 12.8 | С   |

| 16 <u> 10</u> — 2   | 2 | 0.800 x 16 = 12.8 | С   |

| 0 — 10              | А | 0.800 x 16 = 12.8 | С   |

Result of (2598.675)<sub>10</sub> is (A26.ACCC)<sub>16</sub>

# 3. <u>OCTAL NUMBER SYSTEM</u>:-(a)Octal to binary conversion:-

To convert a given a octal number to binary, replace each octal digit by its 3- bit binary equivalent.

For example:

#### Convert (367.52)<sub>8</sub> into binary.

| Solution:<br>Given Octal number is | 3     | 6   | 7   |   | 5   | 2   |

|------------------------------------|-------|-----|-----|---|-----|-----|

| Convert each group octal to binary | = 011 | 110 | 111 | • | 101 | 010 |

Result of (367.52)<sub>8</sub> is (011110111.101010)<sub>2</sub>

### (b)Octal to decimal conversion:-

For conversion octal to decimal number, multiply each digit in the octal number by the weight of its position and add all the product terms

For example: -

# Convert (4057.06) 8 to decimal Solution:

$(4057.06)_8 = 4 \times 8^3 + 0 \times 8^2 + 5 \times 8^1 + 7 \times 8^0 + 0 \times 8^{-1} + 6 \times 8^{-2}$ = 2048 + 0 + 40 + 7 + 0 +0.0937 = (2095. 0937)\_{10}

### Result is (2095.0937)<sub>10</sub> (c) <u>Octal to hexadecimal conversion</u>:-

For conversion of octal to Hexadecimal, first convert the given octal number to binary and then binary number to hexadecimal.

#### For example :-

#### Convert (756.603)<sub>8</sub> to hexadecimal.

| <b>C</b> ~ |    | 410 | -  |   |

|------------|----|-----|----|---|

| So         | าน | แด  | 11 | - |

|   | 7    | 5     | 6         |                                   | 6                                     | 0                                              | 3                                                       |

|---|------|-------|-----------|-----------------------------------|---------------------------------------|------------------------------------------------|---------------------------------------------------------|

| = | 111  | 101   | 110       |                                   | 110                                   | 000                                            | 011                                                     |

| = | 0001 | 1110  | 1110      |                                   | 1100                                  | 0001                                           | 1000                                                    |

| = | 1    | Е     | Е         |                                   | С                                     | 1                                              | 8                                                       |

|   |      | = 111 | = 111 101 | = 111 101 110<br>= 0001 1110 1110 | = 111 101 110 .<br>= 0001 1110 1110 . | = 111 101 110 . 110<br>= 0001 1110 1110 . 1100 | = 111 101 110 . 110 000<br>= 0001 1110 1110 . 1100 0001 |

Result is (1EE.C18)<sub>16</sub>

### (4) <u>HEXADECIMAL NUMBER SYSTEM</u> :-(a) Hexadecimal to binary conversion:-

For conversion of hexadecimal to binary, replace hexadecimal digit by its 4 bit binary group.

#### For example:

#### Convert (3A9E.B0D)<sub>16</sub> into binary.

| <b>Solution:</b><br>Given Hexadecimal number is   | 3      | А    | 9    | Е    |   | В    | 0    | D    |

|---------------------------------------------------|--------|------|------|------|---|------|------|------|

| Convert each hexadecimal<br>digit to 4 bit binary | = 0011 | 1010 | 1001 | 1110 | • | 1011 | 0000 | 1101 |

Result of (3A9E.B0D)<sub>8</sub> is (0011101010011110.101100001101)<sub>2</sub>

# (b)Hexadecimal to decimal conversion:-

For conversion of hexadecimal to decimal, multiply each digit in the hexadecimal number by its position weight and add all those product terms.

#### For example: -Convert (A0F9.0EB)<sub>16</sub> to decimal

#### Solution:

$(A0F9.0EB)_{16} = (10 \times 16^{3}) + (0 \times 16^{2}) + (15 \times 16^{1}) + (9 \times 16^{0}) + (0 \times 16^{-1}) + (14 \times 16^{-2}) + (11 \times 16^{-3})$ = 40960 + 0 + 240 + 9 + 0 + 0.0546 + 0.0026 $= (41209.0572)_{10}$

### Result is (41209.0572)<sub>10</sub> (c) <u>Hexadecimal to Octal conversion</u>:-

For conversion of hexadecimal to octal, first convert the given hexadecimal number to binary and then binary number to octal.

#### For example :-Convert (B9F.AE)<sub>16</sub> to octal.

| Solution :-                       |   |      |     |      |      |      |     |     |

|-----------------------------------|---|------|-----|------|------|------|-----|-----|

| Given hexadecimal no.is           |   | В    | 9   |      | F    | Α    | E   | Ξ   |

| Convert each hex. digit to binary | = | 1011 | 100 | )1 1 | 1111 | 1010 | 11  | 10  |

| Group of 3 bits are               | = | 101  | 110 | 011  | 111  | 101  | 011 | 100 |

| Convert 3 bits group to octal.    | = | 5    | 6   | 3    | 7    | 5    | 3   | 4   |

Result is (5637.534)8

# **BINARY ARITHEMATIC OPERATION** :-

### 1. <u>BINARY ADDITION</u>:-

The binary addition rules are as follows 0 + 0 = 0; 0 + 1 = 1; 1 + 0 = 1; 1 + 1 = 10, i.e 0 with a carry of 1

For example :-

#### Add $(100101)_2$ and $(1101111)_2$ . Solution :-

Result is (10010100)<sub>2</sub>

### 2. <u>BINARY SUBTRACTION</u>:-

The binary subtraction rules are as follows 0 - 0 = 0; 1 - 1 = 0; 1 - 0 = 1; 0 - 1 = 1, with a borrow of 1

#### For example :-Substract $(111.111)_2$ from $(1010.01)_2$ . Solution :-

$\begin{array}{r}

1010.010 \\

- \underline{111.111} \\

\underline{0010.011}

\end{array}$

Result is (0010.011)<sub>2</sub>

### 3. BINARY MULTIPLICATION:-

The binary multiplication rules are as follows  $0 \times 0 = 0$ ;  $1 \times 1 = 1$ ;  $1 \times 0 = 0$ ;  $0 \times 1 = 0$ For example :-

#### Multiply $(1101)_2$ by $(110)_2$ . Solution :-

$$\begin{array}{r}

1101 \\

\times 110 \\

0000 \\

1101 \\

+ 1101 \\

\underline{1001110}

\end{array}$$

Result is (1001110)<sub>2</sub>

### 4. BINARY DIVISION:-

The binary division is very simple and similar to decimal number system. The division by '0' is meaningless. So we have only 2 rules

0 ÷ 1 = 0 1 ÷ 1 = 1 For example :-Divide (10110)<sub>2</sub> by (110)<sub>2</sub>.

Solution :-

Result is (111.1)<sub>2</sub>

# **<u>1's COMPLEMENT REPRESENTATION</u> :-**

The 1's complement of a binary number is obtained by changing each 0 to 1 and each 1 to 0.

### For example :-

Find (1100)<sub>2</sub> 1's complement.

### Solution :-

| Given             | 1 | 1 | 0 | 0 |

|-------------------|---|---|---|---|

| 1's complement is | 0 | 0 | 1 | 1 |

Result is (0011)<sub>2</sub>

# **<u>2's COMPLEMENT REPRESENTATION</u> :-**

The 2's complement of a binary number is a binary number which is obtained by adding 1 to the 1's complement of a number i.e.

2's complement = 1's complement + 1

For example :-

Find (1010)<sub>2</sub> 2's complement.

### Solution :-

| Given             |   | 1 | 0 | 1 | 0 |

|-------------------|---|---|---|---|---|

| 1's complement is |   | 0 | 1 | 0 | 1 |

|                   | + |   |   |   | 1 |

| 2's complement    |   | 0 | 1 | 1 | 0 |

Result is (0110)<sub>2</sub>

# SIGNED NUMBER :-

In sign – magnitude form, additional bit called the sign bit is placed in front of the number. If the sign bit is 0, the number is positive. If it is a 1, the number is negative.

### For example:-

0 1 0 1 0 0 1 = +41  $\uparrow$ Sign bit 1 1 0 1 0 0 1 = -41  $\uparrow$ Sign bit

# **SUBSTRACTION USING COMPLEMENT METHOD** :-

# **<u>1's COMPLEMENT</u>:-**

In 1's complement subtraction, add the 1's complement of subtrahend to the minuend. If there is a carry out, then the carry is added to the LSB. This is called end around carry. If the MSB is 0, the result is positive. If the MSB is 1, the result is negative and is in its 1's complement form. Then take its 1's complement to get the magnitude in binary.

For example:-

Subtract (10000)<sub>2</sub> from (11010)<sub>2</sub> using 1's complement.

Solution:-

|   | 11010 |       | 11010                               |                  | = 26          |

|---|-------|-------|-------------------------------------|------------------|---------------|

| - | 10000 | =>    | + <u>01111</u>                      | (1's complement) | = - <u>16</u> |

|   |       | Carry | $\rightarrow$ <b>1</b> 01001<br>+ 1 |                  | + 10          |

|   |       |       | 01010                               | = +10            |               |

Result is +10

#### **2's COMPLEMENT:-**

In 2's complement subtraction, add the 2's complement of subtrahend to the minuend. If there is a carry out, ignore it. If the MSB is 0, the result is positive. If the MSB is 1, the result is negative and is in its 2's complement form. Then take its 2's complement to get the magnitude in binary.

#### For example:-

### Subtract $(1010100)_2$ from $(1010100)_2$ using 2's complement.

Solution:-

| 1010100                                                       |    | 1010100                                                        | = 84          |  |  |  |

|---------------------------------------------------------------|----|----------------------------------------------------------------|---------------|--|--|--|

| - 1010100                                                     | => | + <u>0101100</u> (2's complement)                              | = - <u>84</u> |  |  |  |

|                                                               |    | <b>1</b> 0 0 0 0 0 0 0 ( Ignore the carry)<br>= 0 (result = 0) |               |  |  |  |

| Hence MSB is 0. The answer is positive. So it is +0000000 = 0 |    |                                                                |               |  |  |  |

# <u>DIGITAL CODES</u>:-

In practice the digital electronics requires to handle data which may be numeric, alphabets and special characters. This requires the conversion of the incoming data into binary format before it can be processed. There is various possible ways of doing this and this process is called encoding. To achieve the reverse of it, we use decoders.

# WEIGHTED AND NON-WEIGHTED CODES:-

There are two types of binary codes

- 1) Weighted binary codes

- 2) Non-weighted binary codes

In weighted codes, for each position (or bit), there is specific weight attached.

For example, in binary number, each bit is assigned particular weight 2n where 'n' is the bit number for n = 0,1,2,3,4 the weights are 1,2,4,8,16 respectively.

Example :- BCD

Non-weighted codes are codes which are not assigned with any weight to each digit position, i.e., each digit position within the number is not assigned fixed value.

Example:- Excess – 3 (XS -3) code and Gray codes

# BINARY CODED DECIMAL (BCD):-

BCD is a weighted code. In weighted codes, each successive digit from right to left represents weights equal to some specified value and to get the equivalent decimal number add the products of the weights by the corresponding binary digit. 8421 is the most common because 8421 BCD is the most natural amongst the other possible codes.

#### For example:-

(567)<sub>10</sub> is encoded in various 4 bit codes.

#### Solution:-

| Decimal   | $\rightarrow$ | 5    | 6    | 7    |

|-----------|---------------|------|------|------|

| 8421 code | $\rightarrow$ | 0101 | 0110 | 0111 |

| 6311 code | $\rightarrow$ | 0111 | 1000 | 1001 |

| 5421 code | $\rightarrow$ | 1000 | 0100 | 1010 |

### **BCD ADDITION:-**

Addition of BCD (8421) is performed by adding two digits of binary, starting from least significant digit. In case if the result is an illegal code (greater than 9) or if there is a carry out of one then add 0110(6) and add the resulting carry to the next most significant.

### For example:-

#### Add 679.6 from 536.8 using BCD addition.

| Sol | u | tio | n: | - |

|-----|---|-----|----|---|

|     | - | _   | -  | - |

| 679.6              | 0110            | 0111    | 1001 . | 0110  | ( 679.6 in BCD)           |

|--------------------|-----------------|---------|--------|-------|---------------------------|

| + <u>536.8</u>     | =>+ <u>0101</u> | 0011    | 0110 . | 1000  | _ (536.8 in BCD)          |

| 1216.4             | 101             | 1 1010  | 1111 . | 1110  | (All are illegal codes)   |

|                    | + 011           | 0 +0110 | +0110  | +0110 | (Add 0110 to each)        |

|                    | 0001 001        | 0001    | 0110 . | 0100  |                           |

|                    | 1 2             | 1       | 6.     | 4     | ( corrected sum = 1216.4) |

| Result is <b>1</b> | 216.4           |         |        |       |                           |

### **BCD SUBTRACTION:-**

The BCD subtraction is performed by subtracting the digits of each 4 - bit group of the subtrahend from corresponding 4 - bit group of the minuend in the binary starting from the LSD. If there is no borrow from the next higher group[ then no correction is required. If there is a borrow from the next group, then  $6_{10}$  (0110) is subtracted from the difference term of this group.

#### For example:-

Subtract 147.8 from 206.7 using 8421 BCD code.

| Solution:-     |                                  |                                |

|----------------|----------------------------------|--------------------------------|

| 206.7          | 0010 0000 0110 .0111             | ( 206.7 in BCD)                |

| - <u>147.8</u> | =>- <u>0001 0100 0111 . 1000</u> | _ (147.8 in BCD)               |

| 58.9           | 0000 1011 1110 . 1111            | (Borrows are present)          |

|                | - 0110 -0110 0110                |                                |

|                | 0101 1000 . 1001                 |                                |

|                | 58.9                             | ( corrected difference = 58.9) |

| Result is (5   | 58.9) <sub>10</sub>              |                                |

# EXCESS THREE(XS-3) CODE:-

The Excess-3 code, also called XS-3, is a non- weighted BCD code. This derives it name from the fact that each binary code word is the corresponding 8421 code word plus 0011(3). It is a sequential code. It is a self complementing code.

# XS-3 ADDITION:-

In XS-3 addition, add the XS-3 numbers by adding the 4 bit groups in each column starting from the LSD. If there is no carry out from the addition of any of the 4 bit groups, subtract 0011 from the sum term of those groups. If there is a carry out, add 0011 to the sum term of those groups

#### For example:-

#### Add 37 and 28 using XS-3 code.

Solution:-

| 37          | 0110 1010             | ( 37 in XS-3)                         |

|-------------|-----------------------|---------------------------------------|

| + <u>28</u> | => + <u>0101 1011</u> | ( 28 in XS-3)                         |

| 65          | 1011 <b>1</b> 1010    | (Carry is generated)                  |

|             | + 1                   | (Propagate carry)                     |

|             | 1100 0101             | (Add 0110 to correct 0101 and         |

|             | - <u>0011 +0011</u>   | subtract 0011 to correct 1100)        |

|             | 1001 1000             | ( Corrected sum in XS-3 = $65_{10}$ ) |

|             |                       |                                       |

#### XS-3 SUBTRACTION:-

To subtract in XS-3 number by subtracting each 4-bit group of the subtrahend from the corresponding 4-bit group of the minuend starting from the LSD. If there is no borrow from the next 4-bit group. add 0011 to the difference term of such groups. If there is a borrow, subtract 0011 from the difference term.

#### For example :-

Subtract 175 from 267 using XS-3 code.

| Solution :-` |    |               |       |       |                                             |

|--------------|----|---------------|-------|-------|---------------------------------------------|

| 267          |    | 0101          | 1010  | 1010  | ( 267 in XS-3)                              |

| <u>-175</u>  | => | - <u>0100</u> | 1010  | 1000  | _ ( 175 in XS-3)                            |

| 092          |    | 0000          | 1111  | 0010  | (Correct 0010 and 0000 by adding 0011 and   |

|              |    | +0011         | -0011 | +0011 | correct 1111 by subtracting 0011)           |

|              |    | 0011          | 1100  | 0101  | (Corrected difference in XS-3 = $92_{10}$ ) |

# ASCII CODE:-

The American Standard Code for Information Interchange (ASCII) pronounced as 'ASKEE' is widely used alphanumeric code. This is basically a 7 bit code. The number of different bit patterns that can be created with 7 bits is 27 = 128, the ASCII can be used to encode both the uppercase and lowercase characters of the alphabet (52 symbols) and some special symbols in addition to the 10 decimal digits. It is used extensively for printers and terminals that interface with small computer systems. The table shown below shows the ASCII groups.

| LSBs |     | MSBs |       |     |     |     |     |     |  |

|------|-----|------|-------|-----|-----|-----|-----|-----|--|

|      | 000 | 001  | 010   | 011 | 100 | 101 | 110 | 111 |  |

| 0000 | NUL | DEL  | Space | 0   | @   | Р   | Р   |     |  |

| 0001 | SOH | DC1  | !     | 1   | A   | Q   | а   | q   |  |

| 0010 | STX | DC2  | "     | 2   | В   | R   | b   | r   |  |

| 0011 | ETX | DC3  | #     | 3   | С   | S   | С   | S   |  |

#### The ASCII code

| 0100 | EOT | DC4 | \$ | 4 | D | Т | d | t   |

|------|-----|-----|----|---|---|---|---|-----|

| 0101 | ENQ | NAK | %  | 5 | E | U | е | u   |

| 0110 | ACK | SYN | &  | 6 | F | V | f | V   |

| 0111 | BEL | ETB | 6  | 7 | G | W | g | W   |

| 1000 | BS  | CAN | (  | 8 | Н | Х | h | х   |

| 1001 | HT  | EM  | )  | 9 | I | Y | i | У   |

| 1010 | LF  | SUB | *  | : | J | Z | j | Z   |

| 1011 | VT  | ESC | +  | ; | К | [ | k | {   |

| 1100 | FF  | FS  | ,  | < | L | ١ | 1 |     |

| 1101 | CR  | GS  | -  | = | М | ] | m | }   |

| 1110 | SO  | RS  | •  | > | Ν | ٨ | n | ~   |

| 1111 | SI  | US  | 1  | ? | 0 | _ | 0 | DLE |

# **EBCDIC CODE:**-

The Extended Binary Coded Decimal Interchange Code (EBCDIC) pronounced as 'eb – si- dik' is an 8 bit alphanumeric code. Since 28 = 256 bit patterns can be formed with 8 bits. It is used by most large computers to communicate in alphanumeric data. The table shown below shows the EBCDIC code.

| LSD<br>(Hex) | MSD(I | Hex) |     |     |    |    |   |   |   |   |   |   |   |   |   |   |

|--------------|-------|------|-----|-----|----|----|---|---|---|---|---|---|---|---|---|---|

|              | 0     | 1    | 2   | 3   | 4  | 5  | 6 | 7 | 8 | 9 | A | В | С | D | E | F |

| 0            | NUL   | DLE  | DS  |     | SP | &  |   |   |   |   |   |   | [ | ] | ١ | 0 |

| 1            | SOH   | DC1  | SOS |     |    |    | / |   | а | j | ~ |   | А | J |   | 1 |

| 2            | STX   | DC2  | FS  | SYN |    |    |   |   | b | k | S |   | В | К | S | 2 |

| 3            | ETX   | DC3  |     |     |    |    |   |   | С | 1 | t |   | С | L | Т | 3 |

| 4            | PF    | RES  | BYP | PN  |    |    |   |   | d | m | u |   | D | М | U | 4 |

| 5            | HT    | NL   | LF  | RS  |    |    |   |   | е | n | v |   | E | Ν | V | 5 |

| 6            | LC    | BS   | EOB | YC  |    |    |   |   | f | 0 | w |   | F | 0 | W | 6 |

| 7            | DEL   | IL   | PRE | EOT |    |    |   |   | g | р | х |   | G | Р | Х | 7 |

| 8            |       | CAN  |     |     |    |    |   |   | h | q | У |   | Н | Q | Y | 8 |

| 9            |       | EM   |     |     |    |    |   |   | i | r | z |   | I | R | Z | 9 |

| А            | SMM   | CC   | SM  |     | Ø  | !  | I | : |   |   |   |   |   |   |   |   |

| В            | VT    |      |     |     | •  | \$ | , | # |   |   |   |   |   |   |   |   |

| С            | FF    | IFS  |     | DC4 | <  | *  | % | @ |   |   |   |   |   |   |   |   |

| D            | CR    | IGS  | ENQ | NAK | (  | )  | _ | 6 |   |   |   |   |   |   |   |   |

| E            | SO    | IRS  | ACK |     | +  | ;  | > | = |   |   |   |   |   | 1 | 1 |   |

| F            | SI    | IUS  | BEL | SUB | 1  | 6  | ? | " |   |   |   |   |   |   |   |   |

#### The EBCDIC code

# **GRAY CODE:**-

The gray code is a non-weighted code. It is not a BCD code. It is cyclic code because successive words in this differ in one bit position only i.e it is a unit distance code.

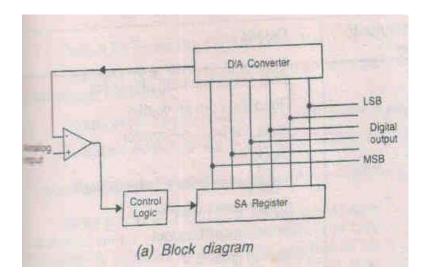

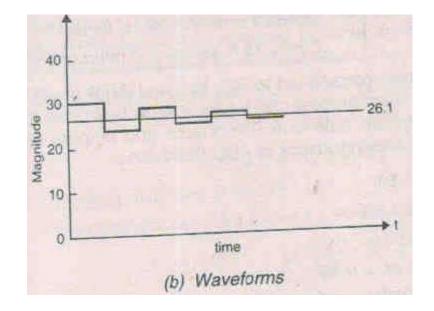

Gray code is used in instrumentation and data acquisition systems where linear or angular displacement is measured. They are also used in shaft encoders, I/O devices, A/D converters and other peripheral equipment.

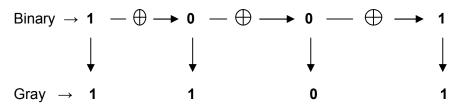

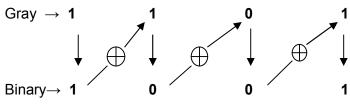

### BINARY- TO - GRAY CONVERSION:-

If an n-bit binary number is represented by  $B_n B_{n-1} - - - B_1$  and its gray code equivalent by  $G_n G_{n-1} - - - - G_1$ , where  $B_n$  and  $G_n$  are the MSBs, then gray code bits are obtained from the binary code as follows

$G_{n} = B_{n}$   $G_{n-1} = B_{n} \oplus B_{n-1}$   $\vdots$   $G_{1} = B_{2} \oplus B_{1}$

Where the symbol  $\oplus$  stands for Exclusive OR (X-OR)

#### For example :-

Convert the binary 1001 to the Gray code.

Solution :-`

The gray code is **1101**

### **GRAY- TO - BINARY CONVERSION:-**

If an n-bit gray number is represented by  $G_n G_{n-1} - --- G_1$  and its binary equivalent by  $B_n B_{n-1} - --- B_1$ , then binary bits are obtained from Gray bits as follows :

$B_{n} = G_{n}$   $B_{n-1} = B_{n} \oplus G_{n-1}$   $\vdots$   $B_{1} = B_{2} \oplus G_{1}$

For example :-Convert the Gray code 1101 to the binary.

Solution :-

The binary code is 1001

# LOGIC GATES

# LOGIC GATES:-

- Logic gates are the fundamental building blocks of digital systems.

- There are 3 basic types of gates AND, OR and NOT.

- Logic gates are electronic circuits because they are made up of a number of electronic devices and components.

- Inputs and outputs of logic gates can occur only in 2 levels. These two levels are termed HIGH and LOW, or TRUE and FALSE, or ON and OFF or simply 1 and 0.

- The table which lists all the possible combinations of input variables and the corresponding outputs is called a truth table.

# LEVEL LOGIC:-

A logic in which the voltage levels represents logic 1 and logic 0. Level logic may be positive or negative logic. **Positive Logic:**-

A positive logic system is the one in which the higher of the two voltage levels represents the logic 1 and the lower of the two voltages level represents the logic 0.

### Negative Logic:-

A negative logic system is the one in which the lower of the two voltage levels represents the logic 1 and the higher of the two voltages level represents the logic 0.

# DIFFERENT TYPES OF LOGIC GATES:-

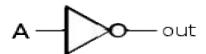

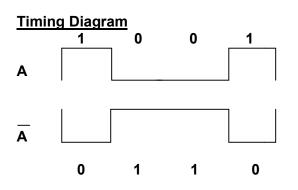

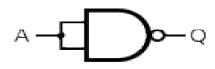

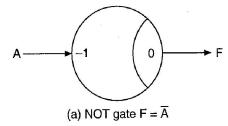

# NOT GATE (INVERTER):-

- A NOT gate, also called and inverter, has only one input and one output.

- It is a device whose output is always the complement of its input.

- The output of a NOT gate is the logic 1 state when its input is in logic 0 state and the logic 0 state when its inputs is in logic 1 state.

### IC No. :- 7404

Logic Symbol

| INPUT<br>A | OU <u>T</u> PUT<br>A |

|------------|----------------------|

| 0          | 1                    |

| 1          | 0                    |

Truth table

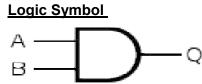

# AND GATE:-

- An AND gate has two or more inputs but only one output.

- The output is logic 1 state only when each one of its inputs is at logic 1 state.

- The output is logic 0 state even if one of its inputs is at logic 0 state.

# IC No.:- 7408

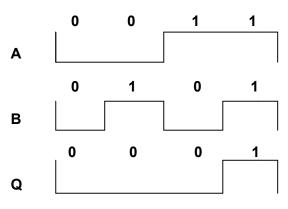

# Timing Diagram

| Truth Table |   |         |  |  |  |

|-------------|---|---------|--|--|--|

|             |   | OUTPUT  |  |  |  |

| Α           | В | Q=A . B |  |  |  |

| 0           | 0 | 0       |  |  |  |

| 0           | 1 | 0       |  |  |  |

| 1           | 0 | 0       |  |  |  |

| 1           | 1 | 1       |  |  |  |

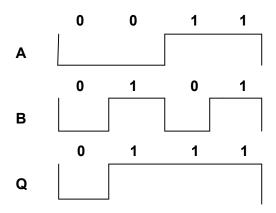

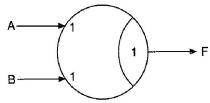

# OR GATE:-

- An OR gate may have two or more inputs but only one output.

- The output is logic 1 state, even if one of its input is in logic 1 state.

- The output is logic 0 state, only when each one of its inputs is in logic state.

#### IC No.:- 7432 Logic Symbol

# **Truth Table**

| INF | PUT | OUTPUT  |

|-----|-----|---------|

| Α   | В   | Q=A + B |

| 0   | 0   | 0       |

| 0   | 1   | 1       |

| 1   | 0   | 1       |

| 1   | 1   | 1       |

### Timing Diagram

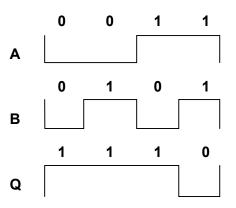

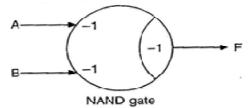

# NAND GATE:-

- NAND gate is a combination of an AND gate and a NOT gate.

- The output is logic 0 when each of the input is logic 1 and for any other combination of inputs, the output is logic 1.

## IC No.:- 7400 two input NAND gate 7410 three input NAND gate 7420 four input NAND gate

7430 eight input NAND gate

### Logic Symbol

## Truth Table

| INPUT |   | OUTPUT |  |  |

|-------|---|--------|--|--|

| Α     | В | Q= A.B |  |  |

| 0     | 0 | 1      |  |  |

| 0     | 1 | 1      |  |  |

| 1     | 0 | 1      |  |  |

| 1     | 1 | 0      |  |  |

### **Timing Diagram**

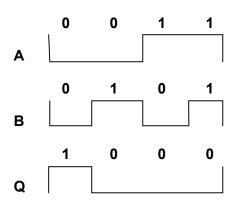

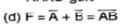

# NOR GATE:-

- NOR gate is a combination of an OR gate and a NOT gate.

- The output is logic 1, only when each one of its input is logic 0 and for any other combination of inputs, the output is a logic 0 level.

### IC No.:- 7402 two input NOR gate 7427 three input NOR gate 7425 four input NOR gate

### Logic Symbol

### Truth Table

| IN | PUT | OUTPUT   |

|----|-----|----------|

| Α  | В   | Q= A + B |

| 0  | 0   | 1        |

| 0  | 1   | 0        |

| 1  | 0   | 0        |

| 1  | 1   | 0        |

### Timing Diagram

# EXCLUSIVE - OR (X-OR) GATE:-

- An X-OR gate is a two input, one output logic circuit.

- The output is logic 1 when one and only one of its two inputs is logic 1. When both the inputs is logic 0 or when both the inputs is logic 1, the output is logic 0.

### IC No.:- 7486

Logic Symbol

INPUTS are **A** and **B**

OUTPUT is  $\mathbf{Q} = \mathbf{A} \bigoplus \mathbf{B}$

$= A \overline{B} + A \overline{B}$

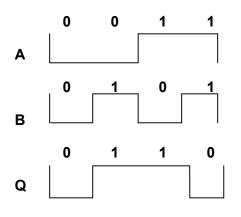

# Timing Diagram

# Truth Table

| INF | VUT | OUTPUT                         |  |  |

|-----|-----|--------------------------------|--|--|

| Α   | В   | <b>Q</b> = <b>A</b> ⊕ <b>B</b> |  |  |

| 0   | 0   | 0                              |  |  |

| 0   | 1   | 1                              |  |  |

| 1   | 0   | 1                              |  |  |

| 1   | 1   | 0                              |  |  |

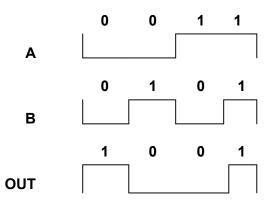

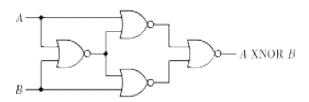

# EXCLUSIVE - NOR (X-NOR) GATE:-

- An X-NOR gate is the combination of an X-OR gate and a NOT gate.

- An X-NOR gate is a two input, one output logic circuit.

- The output is logic 1 only when both the inputs are logic 0 or when both the inputs is 1.

- The output is logic 0 when one of the inputs is logic 0 and other is 1.

Logic Symbol

OUT =  $A B + \overline{A} \overline{B}$

= A XNOR B

### Timing Diagram

# **UNIVERSAL GATES:-**

There are 3 basic gates AND, OR and NOT, there are two universal gates NAND and NOR, each of which can realize logic circuits single handedly. The NAND and NOR gates are called universal building blocks. Both NAND and NOR gates can perform all logic functions i.e. AND, OR, NOT, EXOR and EXNOR.

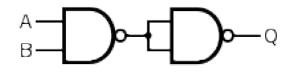

# NAND GATE:-

a) Inverter from NAND gate

Input = AOutput  $Q = \overline{A}$

b) AND gate from NAND gate

Input s are **A** and **B** Output **Q** = **A**.**B**

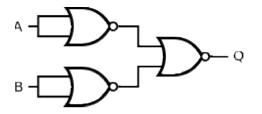

### c) OR gate from NAND gate

Inputs are **A** and **B** Output **Q** = **A**+**B**

| INPUT |   | OUTPUT        |  |  |

|-------|---|---------------|--|--|

| Α     | В | OUT =A XNOR B |  |  |

| 0     | 0 | 1             |  |  |

| 0     | 1 | 0             |  |  |

| 1     | 0 | 0             |  |  |

| 1     | 1 | 1             |  |  |

#### d) NOR gate from NAND gate

Inputs are  $\mathbf{A}$  and  $\mathbf{B}$ Output  $\mathbf{Q} = \mathbf{A} + \mathbf{B}$

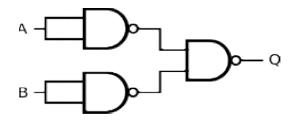

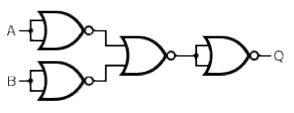

### e) EX-OR gate from NAND gate

Inputs are A and B Output Q = AB + AB

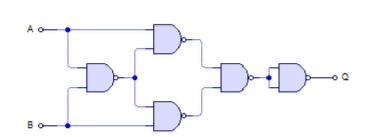

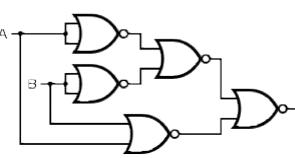

### f) EX-NOR gate From NAND gate

Inputs are A and B Output Q = A B +  $\overline{A} \overline{B}$

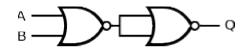

# NOR GATE:-

a) Inverter from NOR gate Input = <u>A</u> Output Q = A

b) AND gate from NOR gate Input s are A and B Output Q = A.B

#### c) OR gate from NOR gate

Inputs are **A** and **B** Output **Q** = **A+B**

#### d) NAND gate from NOR gate

Inputs are **A** and **B** Output **Q** =  $\overline{\mathbf{A}.\mathbf{B}}$

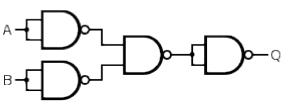

e) EX-OR gate from NOR gate

Inputs are A and B Output Q = AB + AB

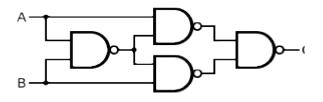

# f) EX-NOR gate From NOR gate

Inputs are A and B \_\_\_\_\_ Output Q = A B +  $\overline{A} \overline{B}$

# THRESHOLD LOGIC:-

# **INTRODUCTION:-**

- The threshold element, also called the threshold gate (T-gate) is a much more powerful device than any of the conventional logic gates such as NAND, NOR and others.

- Complex, large Boolean functions can be realized using much fewer threshold gates.

- Frequently a single threshold gate can realize a very complex function which otherwise might require a large number of conventional gates.

- T-gate offers incomparably economical realization; it has not found extensive use with the digital system designers mainly because of the following limitations.

- 1. It is very sensitive to parameter variations.

- 2. It is difficult to fabricate it in IC form.

3. The speed of switching of threshold elements in much lower than that of conventional gates.

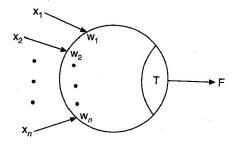

# THE THRESHOLD ELEMENTS:-

- A threshold element or gate has 'n' binary inputs x<sub>1</sub>, x<sub>2</sub>, ...., x<sub>n</sub>; and a single binary output F. But in addition to those, it has two more parameters.

- Its parameters are a threshold T and weights w<sub>1</sub>, w<sub>2</sub>, ..., w<sub>n</sub>. The weights w<sub>1</sub>, w<sub>2</sub>, ..., w<sub>n</sub> are associated with the input variables x<sub>1</sub>, x<sub>2</sub>, ..., x<sub>n</sub>.

- The value of the threshold (T) and weights may be real, positive or negative number.

- The symbol of the threshold element is shown in fig.(a).

- It is represented by a circle partitioned into two parts, one part represents the weights and other represents T.

- It is defined as

$F(x_1, x_2, \dots, x_n) = 1 \text{ if and only if } \sum_{i=1}^{n} w_i x_i \ge T$ otherwise

$F(x_1, x_2, ..., x_n) = 0$

• The sum and product operation are normal arithmetic operations and the sum  $\sum_{i=1}^{n} w_i x_i \ge T$

is called the weighted sum of the element or gate.

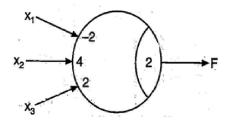

Example:-

Obtain the minimal Boolean expression from the threshold gate shown in figure.

#### Solution:-

The threshold gate with three inputs  $x_1$ ,  $x_2$ ,  $x_3$  with weights  $-2(w_1)$ ,  $4(w_2)$  and  $2(w_3)$  respectively. The value of threshold is 2(T). The table shown is the weighted sums and outputs for all input combinations. For this threshold gate, the weighted sum is

$$w = w_1 x_1 + w_2 x_2 + w_3 x_3$$

= (-2)x<sub>1</sub> + (4)x<sub>2</sub> + (2)x<sub>3</sub>

= -2x<sub>1</sub> + 4x<sub>2</sub> + 2x<sub>3</sub>

The output F is logic 1 for w≥2 and it is logic 0 for w<2

| Input Variables       |                       |            | Weighted Sum              | Output |

|-----------------------|-----------------------|------------|---------------------------|--------|

| <b>X</b> <sub>1</sub> | <b>X</b> <sub>2</sub> | <b>X</b> 3 | $w = -2x_1 + 4x_2 + 2x_3$ | F      |

| 0                     | 0                     | 0          | 0                         | 0      |

| 0                     | 0                     | 1          | 2                         | 1      |

| 0                     | 1                     | 0          | 4                         | 1      |

| 0                     | 1                     | 1          | 6                         | 1      |

| 1                     | 0                     | 0          | -2                        | 0      |

| 1                     | 0                     | 1          | 0                         | 0      |

| 1                     | 1                     | 0          | 2                         | 1      |

| 1                     | 1                     | 1          | 4                         | 1      |

From the input – output relation is given in the table, the Boolean expression for the output is

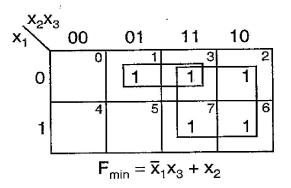

F=∑ m (1, 2, 3, 6, 7)

The K-map for F is

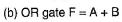

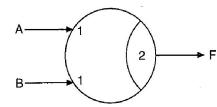

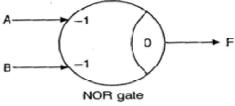

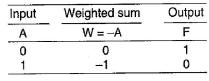

# UNIVERSALITY OF A T-GATE:-

- A single T-gate can realize a large number of functions by merely changing either the weights or the threshold or both, which can be done by altering the value of the corresponding resistors.

- Since a threshold gate can realize universal gates, i.e., NAND gates and NOR gates, a threshold gate is also a universal gate.

- Single threshold gate cannot realize by a single T-gate

- Realization of logic gates using T-gates is shown in the below figure.

(c) AND gate F = AB

(e)

$$F = \overline{A} \cdot \overline{B} = \overline{A + B}$$

| Inputs |   | Weighted sum | Output |  |

|--------|---|--------------|--------|--|

| A      | В | w = A + B    | F      |  |

| 0      | 0 | 0            | 0      |  |

| 0      | 1 | 1            | 1      |  |

| 1      | 0 | 1            | 1      |  |

| 1      | 1 | 2            | 1      |  |

| Inputs<br>A B |   | puts Weighted sum |   |

|---------------|---|-------------------|---|

|               |   | w = A + B         | F |

| 0             | 0 | 0                 | 0 |

| 0             | 1 | 1                 | 0 |

| 1             | 0 | 1                 | 0 |

| 1             | 1 | 2                 | 1 |

| Inputs |   | Weighted sum | Output |  |

|--------|---|--------------|--------|--|

| A      | в | w = -A - B   | F      |  |

| 0      | 0 | 0            | 1      |  |

| 0      | 1 | -1           | 1      |  |

| 1      | 0 | -1           | 1      |  |

| 1      | 1 | -2           | 0      |  |

| Inpute |   | Weighted sum | Output |  |

|--------|---|--------------|--------|--|

| A B    |   | w = -A - B   | F      |  |

| 0      | 0 | 0            | 1      |  |

| 0      | 1 | 1            | 0      |  |

| 1      | 0 | -1           | 0      |  |

| 1      | 1 | -2           | 0      |  |

| Inputs |   | Weighted sum | Output |  |

|--------|---|--------------|--------|--|

| A      | в | w = -A + B   | F      |  |

| 0      | 0 | 0            | 0      |  |

| ō      | 1 | 1            | 1      |  |

| 1      | 0 | -1           | 0      |  |

| 1      | 1 | 0            | 0      |  |

| Inputs |   | Weighted sum | Output |  |

|--------|---|--------------|--------|--|

| A      | в | w = A - B    | F      |  |

| 0      | 0 | 0            | 0      |  |

| 0      | 1 | -1           | 0      |  |

| 1      | 0 | 1            | 1      |  |

| 1      | 1 | 0            | 0      |  |

sum Outr

# **BOOLEAN ALGEBRA**

# **INTRODUCTION:-**

- Switching circuits are also called logic circuits, gates circuits and digital circuits.

- Switching algebra is also called Boolean algebra.

- Boolean algebra is a system of mathematical logic. It is an algebraic system consisting of the set of elements (0,1), two binary operators called OR and AND and unary operator called NOT.

- It is the basic mathematical tool in the analysis and synthesis of switching circuits.

- It is a way to express logic functions algebraically.

- Any complex logic can be expressed by a Boolean function.

- The Boolean algebra is governed by certain well developed rules and laws.

# AXIOMS AND LAWS OF BOOLEAN ALGEBRA:-

Axioms or postulates of Boolean algebra are set of logical expressions that are accepted without proof and upon which we can build a set of useful theorems. Actually, axioms are nothing more than the definitions of the three basic logic operations AND, OR and INVERTER. Each axiom can be interpreted as the outcome of an operation performed by a logic gate.

| AND operation      | OR operation         | NOT operation               |

|--------------------|----------------------|-----------------------------|

| Axiom 1: 0 . 0 = 0 | Axiom 5: $0 + 0 = 0$ | Axiom 9: $\overline{1} = 0$ |

| Axiom 2: 0 . 1 = 0 | Axiom 6: 0 + 1 = 1   | Axiom $10:\overline{0} = 1$ |

| Axiom 3: 1 . 0 = 0 | Axiom 7: 1 + 0 = 1   |                             |

| Axiom 2: 1 . 1 = 1 | Axiom 8: 1 + 1 = 1   |                             |

### 1. Complementation Laws:-

The term complement simply means to invert, i.e. to changes 0s to 1s and 1s to 0s. The five laws of complementation are as follows:

**Law 1:** 0 = 1 Law 2: 1 = 0 Law 3: if A = 0, then A = 1 Law 4: if <u>A</u> = 1,thenA = 0 **Law 5:**  $\overline{A} = 0$  (double complementation law) 2. OR Laws:-The four OR laws are as follows **Law 1:** A + 0 = 0(Null law) **Law 2:** A + 1 = 1(Identity law) Law 3: A + A = A **Law 4:**  $A + \overline{A} = 1$ 3. AND Laws:-The four AND laws are as follows **Law 1:** A . 0 = 0(Null law) **Law 2:** A . 1 = 1(Identity law) Law 3: A . A = A Law 4:  $A \cdot \overline{A} = 0$

#### 4. Commutative Laws:-

Commutative laws allow change in position of AND or OR variables. There are two commutative laws.

=

=

**Law 1:** A + B = B + A **Proof**

| Α | В | A + B |

|---|---|-------|

| 0 | 0 | 0     |

| 0 | 1 | 1     |

| 1 | 0 | 1     |

| 1 | 1 | 1     |

| В | Α | B+ A |

|---|---|------|

| 0 | 0 | 0    |

| 0 | 1 | 1    |

| 1 | 0 | 1    |

| 1 | 1 | 1    |

Law 2: A . B = B . A

Proof

| Α | В | А.В |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

| В | Α | В. А |

|---|---|------|

| 0 | 0 | 0    |

| 0 | 1 | 0    |

| 1 | 0 | 0    |

| 1 | 1 | 1    |

This law can be extended to any number of variables. For example A.B. C = B. C. A = C. A. B = B. A. C

### 5. Associative Laws:-

The associative laws allow grouping of variables. There are 2 associative laws. Law 1: (A + B) + C = A + (B + C)

=

#### Proof

| Α | В | С | A+B | (A+B)+C |

|---|---|---|-----|---------|

| 0 | 0 | 0 | 0   | 0       |

| 0 | 0 | 1 | 0   | 1       |

| 0 | 1 | 0 | 1   | 1       |

| 0 | 1 | 1 | 1   | 1       |

| 1 | 0 | 0 | 1   | 1       |

| 1 | 0 | 1 | 1   | 1       |

| 1 | 1 | 0 | 1   | 1       |

| 1 | 1 | 1 | 1   | 1       |

| Α | В | С | B+C | A+(B+C) |

|---|---|---|-----|---------|

| 0 | 0 | 0 | 0   | 0       |

| 0 | 0 | 1 | 1   | 1       |

| 0 | 1 | 0 | 1   | 1       |

| 0 | 1 | 1 | 1   | 1       |

| 1 | 0 | 0 | 0   | 1       |

| 1 | 0 | 1 | 1   | 1       |

| 1 | 1 | 0 | 1   | 1       |

| 1 | 1 | 1 | 1   | 1       |

Law 2: (A .B) C = A (B .C)

Proof

| Α | В | С | AB | (AB)C |

|---|---|---|----|-------|

| 0 | 0 | 0 | 0  | 0     |

| 0 | 0 | 1 | 0  | 0     |

| 0 | 1 | 0 | 0  | 0     |

| 0 | 1 | 1 | 0  | 0     |

| 1 | 0 | 0 | 0  | 0     |

| 1 | 0 | 1 | 0  | 0     |

| 1 | 1 | 0 | 1  | 0     |

| 1 | 1 | 1 | 1  | 1     |

| Α | В | С | B.C | A(B.C) |

|---|---|---|-----|--------|

| 0 | 0 | 0 | 0   | 0      |

| 0 | 0 | 1 | 0   | 0      |

| 0 | 1 | 0 | 0   | 0      |

| 0 | 1 | 1 | 1   | 0      |

| 1 | 0 | 0 | 0   | 0      |

| 1 | 0 | 1 | 0   | 0      |

| 1 | 1 | 0 | 0   | 0      |

| 1 | 1 | 1 | 1   | 1      |

This law can be extended to any number of variables. For example

A(BCD) = (ABC)D = (AB) (CD)

# 6. Distributive Laws:-

The distributive laws allow factoring or multiplying out of expressions. There are two distributive laws.

=

**Law 1:** A (B + C) = AB + AC

Proof

| Α | В | С | B+C | A(B+C) |

|---|---|---|-----|--------|

| 0 | 0 | 0 | 0   | 0      |

| 0 | 0 | 1 | 1   | 0      |

| 0 | 1 | 0 | 1   | 0      |

| 0 | 1 | 1 | 1   | 0      |

| 1 | 0 | 0 | 0   | 0      |

| 1 | 0 | 1 | 1   | 1      |

| 1 | 1 | 0 | 1   | 1      |

| 1 | 1 | 1 | 1   | 1      |

=

| Α | В | С | AB | AC | A+(B+C) |

|---|---|---|----|----|---------|

| 0 | 0 | 0 | 0  | 0  | 0       |

| 0 | 0 | 1 | 0  | 0  | 0       |

| 0 | 1 | 0 | 0  | 0  | 0       |

| 0 | 1 | 1 | 0  | 0  | 0       |

| 1 | 0 | 0 | 0  | 0  | 0       |

| 1 | 0 | 1 | 0  | 1  | 1       |

| 1 | 1 | 0 | 1  | 0  | 1       |

| 1 | 1 | 1 | 1  | 1  | 1       |

Law 2: A + BC = (A+B) (A+C)Proof RHS = (A+B) (A+C) = AA + AC + BA + BC = A + AC + AB + BC = A (1+C+B) + BC = A (1+C+B) + BC = A (1+C+B) + BC = A + BC = LHS7. Redundant Literal Rule (RLR):-Law 1:  $A + \overline{AB} = A + B$  Proof

$$A + \overline{A}B = (A + \overline{A}) (A + B)$$

$$= 1. (A + B)$$

$$= A + B$$

Proof

$A(\overline{A} + B) = A\overline{A} + AB$ = 0 + AB= AB

#### 8. Idempotence Laws:-

Idempotence means same value.

Law 1: A. A = A

#### Proof

If A = 0, then A. A = 0. 0 = 0 = AIf A = 1, then A. A = 1. 1 = 1 = AThis law states that AND of a variable with itself is equal to that variable only.

Law 2: A + A = A

#### Proof

If A = 0, then A + A = 0 + 0 = 0 = AIf A = 1, then A + A = 1 + 1 = 1 = AThis law states that OR of a variable with itself is equal to that variable only.

#### 9. Absorption Laws:-

There are two laws:

#### Proof

$A + A \cdot B = A (1 + B) = A \cdot 1 = A$

| Α | В | AB | A+AB |

|---|---|----|------|

| 0 | 0 | 0  | 0    |

| 0 | 1 | 0  | 0    |

| 1 | 0 | 0  | 1    |

| 1 | 1 | 1  | 1    |

#### Law 2: A ( A + B) = A

Proof

$A (A + B) = A \cdot A + A \cdot B = A + AB = A(1 + B) = A \cdot 1 = A$

| Α | В | A+B | A(A+B) |

|---|---|-----|--------|

| 0 | 0 | 0   | 0      |

| 0 | 1 | 1   | 0      |

| 1 | 0 | 1   | 1      |

| 1 | 1 | 1   | 1      |

#### 10. Consensus Theorem (Included Factor Theorem):-

Theorem 1:  $AB + \overline{AC} + BC = AB + \overline{AC}$ Proof **LHS =** AB + AC + BC= AB + AC + BC (A+A) $= AB + \overline{A}C + BCA + BC\overline{A}$ = AB (1 + C) + AC (1 + B)=AB (1) +AC (1)  $= AB + \overline{A}C$ = RHS Theorem 2:  $(A + B)(\overline{A} + C)(B + C) = (A + B)(\overline{A} + C)$ Proof LHS =  $(A + B)(\overline{A} + C)(B + C)$  $= (\overline{AA} + AC + \overline{BA} + BC) (B + C)$ = (AC + BC + $\overrightarrow{AB}$ ) (B + C)  $= ABC + BC + \overline{AB} + AC + BC + \overline{ABC}$  $= AC + BC + \overline{AB}$ RHS=  $(A + B)(\overline{A}+C)$  $= A\overline{A} + AC + BC + \overline{AB}$  $= AC + BC + \overline{AB}$ = LHS 11. Transposition Theorem:-Theorem: AB + AC = (A + C)(A + B)Proof **RHS=** (A + C)  $(\overline{A} + B)$  $= \overrightarrow{AA} + \overrightarrow{CA} + AB + CB$  $= 0 + \overrightarrow{AC} + AB + BC$ = AC + AB + BC (A+A)= AB + ABC + AC + ABC= AB + AC= LHS

#### 12. De Morgan's Theorem:-

De Morgan's theorem represents two laws in Boolean algebra.

Law 1:  $\overline{A + B} = \overline{A \cdot B}$

| Α | В | A + B | A + B |

|---|---|-------|-------|

| 0 | 0 | 0     | 1     |

| 0 | 1 | 1     | 0     |

| 1 | 0 | 1     | 0     |

| 1 | 1 | 1     | 0     |

| Α | В | Ā | В | AB |

|---|---|---|---|----|

| 0 | 0 | 1 | 1 | 1  |

| 0 | 1 | 1 | 0 | 0  |

| 1 | 0 | 0 | 1 | 0  |

| 1 | 1 | 0 | 0 | 0  |

=

This law states that the complement of a sum of variables is equal to the product of their individual complements.

Law 2:  $\overline{A \cdot B} = \overline{A} + \overline{B}$ Proof

|         |     | В | Α | В |

|---------|-----|---|---|---|

|         | 0   | 0 | 1 | 1 |

| 0 1 0 1 | 0   | 1 | 1 | 0 |

| 1 0 0 1 | = 0 | 0 | 0 | 1 |

| 1 1 1 0 | 1   | 1 | 0 | 0 |

This law states that the complement of a product of variables is equal to the sum of their individual complements.

# **DUALITY:-**

The implication of the duality concept is that once a theorem or statement is proved, the dual also thus stand proved. This is called the principle of duality.

$[f (A, B, C, ..., 0, 1, +, \cdot)]_d = f(A, B, C, ..., 1, 0, \cdot, +)$ Relations between complement and dual

$f_c$  (A, B, C, ....) = f (A, B, C, ....) =  $f_d$  ( $\overline{A}$ ,  $\overline{B}$ ,  $\overline{C}$ ,...)

$f_d$  (A, B, C, ....) = f ( $\overline{A}, \overline{B}, \overline{C}, ...$ ) =  $f_c$  ( $\overline{A}, \overline{B}, \overline{C}, ....$ )

The first relation states that the complement of a function f(A, B, C, ...) can be obtained by complementing all the variables in the dual function  $f_d(A, B, C, ....)$ .

Dual

The second relation states that the dual can be obtained by complementing all the literals in f(A, B, C, ...).

DUALS:-

Given expression

| 0 = 1                                                                             | 1 = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0 ·1 = 0                                                                          | 1 + 0 = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $0 \cdot 0 = 0$                                                                   | 1 + 1 = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1 ·1 = 1                                                                          | 0 + 0 = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $A \cdot 0 = 0$                                                                   | A + 1 = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $A \cdot 1 = A$                                                                   | A + 0 = A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $A \cdot A = A$                                                                   | A + A = A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $A \cdot \overline{A} = 0$                                                        | $A + \overline{A} = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $A \cdot B = B \cdot A$                                                           | A + B = B+ A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $A \cdot (B \cdot C) = (A \cdot B) \cdot C$                                       | A + (B + C) = (A + B) + C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $A \cdot (B + C) = AB + AC$                                                       | A + BC = (A + B) (A + C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A( A + B ) = A                                                                    | A + AB = A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $\underline{A} \cdot (\underline{A} \cdot \underline{B}) = A \cdot \underline{B}$ | A + A + B = A + B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AB = A + B                                                                        | A + B = A B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $(A + B) (\overline{A} + C) (B + C) = (A + B) (\overline{A} + C)$                 | $AB + \overline{A}C + BC = AB + \overline{A}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A + BC = (A + B)(A + C)                                                           | $A(B^{+}+C) = AB^{+}+AC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $(A+C)(\overline{A}+B) = AB+\overline{A}C$                                        | AC+AB=(A+B) (A+C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| (A+B)(C+D) = AC + AD + BC + BD                                                    | (AB+CD) = (A+C)(A+D)(B+C)(B+D)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $\underline{A + B} = \underline{AB + AB}$                                         | A <u>B =(A+B) (A+B)</u> (A+ <del>B)</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $\overline{AB} + \overline{A} + AB = 0$                                           | $\overline{A + B} \cdot \overline{A} \cdot (A + B) = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                   | $0 \cdot 1 = 0$<br>$0 \cdot 0 = 0$<br>$1 \cdot 1 = 1$<br>$A \cdot 0 = 0$<br>$A \cdot 1 = A$<br>$A \cdot A = A$<br>$A \cdot \overline{A} = 0$<br>$A \cdot B = B \cdot A$<br>$A \cdot (B \cdot C) = (A \cdot B) \cdot C$<br>$A \cdot (B + C) = AB + AC$<br>A (A + B) = A<br>$A \cdot (A \cdot B) = A \cdot B$<br>$\overline{AB} = \overline{A} + B$<br>$(A + B) (\overline{A} + C) (B + C) = (A + B)(\overline{A} + C)$<br>$A + \overline{BC} = (A + \overline{B})(A + C)$<br>$(A + C)(\overline{A} + B) = AB + \overline{AC}$<br>(A + B)(C + D) = AC + AD + BC + BD<br>$\underline{A + B} = AB + \overline{AB} + \overline{AB}$ |

# SUM - OF - PRODUCTS FORM:-

- This is also called disjunctive Canonical Form (DCF) or Expanded Sum of Products Form or Canonical Sum of Products Form.

- In this form, the function is the sum of a number of products terms where each product term contains all variables of the function either in complemented or uncomplemented form.

- This can also be derived from the truth table by finding the sum of all the terms that corresponds to those combinations for which 'f' assumes the value 1.

For example

$f(A, B, C) = \overline{AB} + \overline{BC}$  $= \overline{AB} (C + \overline{C}) + \overline{BC} (A + \overline{A})$  $= \overline{A} \overline{BC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

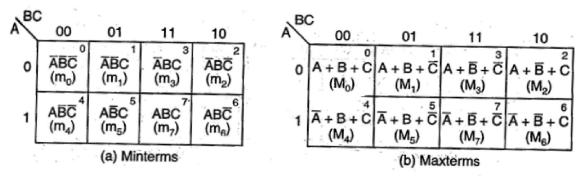

- The product term which contains all the variables of the functions either in complemented or uncomplemented form is called a minterm.

- The minterm is denoted as mo, m1, m2 ....

- An 'n' variable function can have 2n minterms.

- Another way of representing the function in canonical SOP form is the showing the sum of minterms for which the function equals to 1.

For example

```

f (A, B, C) = m_1 + m_2 + m_3 + m_5

or

```

$f(A, B, C) = \sum m(1, 2, 3, 5)$

where  $\sum$ m represents the sum of all the minterms whose decimal codes are given the parenthesis.

# PRODUCT- OF - SUMS FORM:-

- This form is also called as Conjunctive Canonical Form (CCF) or Expanded Product of Sums Form or Canonical Product Of Sums Form.

- This is by considering the combinations for which f = 0

- Each term is a sum of all the variables.

- The function f (A, B, C) =  $(\overline{A} + \overline{B} + C \cdot \overline{C}) + (A + B + C \cdot \overline{C})$

$$= (\overline{A} + \overline{B} + C) (\overline{A} + \overline{B} + \overline{C}) (A + B + C) (A + B + \overline{C})$$

- The sum term which contains each of the 'n' variables in either complemented or uncomplemented form is called a maxterm.

- Maxterm is represented as M<sub>0</sub>, M<sub>1</sub>, M<sub>2</sub>, ..... Thus CCF of 'f' may be written as

f(A, B, C)=  $M_0 \cdot M_4 \cdot M_6 \cdot M_7$ or

f(A, B, C) = ( 0, 4, 6, 7)

Where represented the product of all maxterms.

# **CONVERSION BETWEEN CANONICAL FORM:-**

The complement of a function expressed as the sum of minterms equals the sum of minterms missing from the original function.

Example:-

$f(A, B, C) = \sum m(0,2,4,6,7)$ This has a complement that can be expressed as

$f(\overline{A, B, C}) = \sum m(1, 3, 5) = m_1 + m_3 + m_5$ If we complement f by De- Morgan's theorem we obtain 'f' in a form.  $f = (\overline{m_1 + m_3 + m_5}) = \overline{m_1} \cdot \overline{m_3} \cdot \overline{m_5}$

### Example:-

# Expand A (A + B) (A + B + C) to maxterms and minterms. Solution:-

In POS form  $A(\overline{A} + B)(\overline{A} + B + \overline{C})$ A = A + B B + CC $= (A + B) (A + B) + C \cdot C$ = (A + B + CC) (A + B + CC)=  $(A + B + C) (A + B + \overline{C}) (A + \overline{B} + C) (A + \overline{B} + \overline{C})$  $A + B = A + B + C \cdot C$  $= (\overline{A} + B + C) (\overline{A} + B + \overline{C})$ Therefore  $A(\overline{A} + B)(\overline{A} + B + \overline{C})$  $= (A + B + C) (A + B + \overline{C}) (A + \overline{B} + C) (A + \overline{B} + C) (\overline{A + B} + C) (\overline{A + B} + C) (\overline{A + B} + C)$ = (000) (001) (010) (011) (100) (101) $= M_0 \cdot M_1 \cdot M_2 \cdot M_3 \cdot M_4 \cdot M_5$ =∏ M( 0, 1, 2, 3, 4,5)

The maxterms  $M_6$  and  $M_7$  are missing in the POS form.

So, the SOP form will contain the minterms 6 and 7

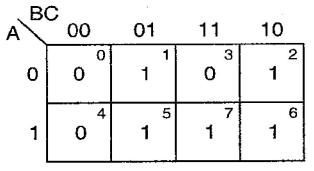

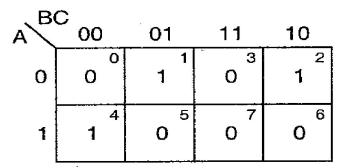

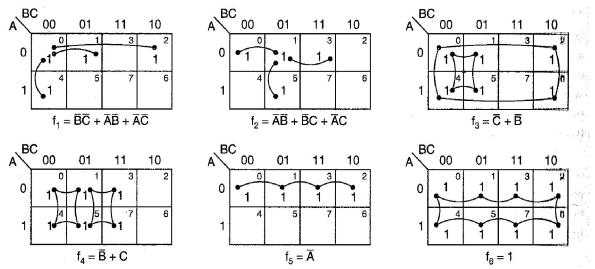

# KARNAUGH MAP OR K- MAP:-

- The K- map is a chart or a graph, composed of an arrangement of adjacent cells, each representing a particular combination of variables in sum or product form.

- The K- map is systematic method of simplifying the Boolean expression. •

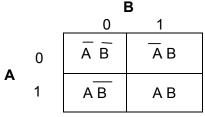

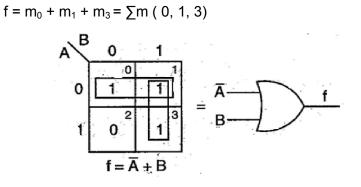

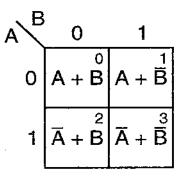

# **TWO VARIABLE K- MAP:-**

A two variable expression can have  $2^2 = 4$  possible combinations of the input variables A and B.

# Mapping of SOP Expression:-

- The 2 variable K-map has  $2^2 = 4$  squares. These squares are called cells.

- A '1' is placed in any square indicates that corresponding minterm is included in the output expression, and a 0 or no entry in any square indicates that the corresponding minterm does not appear in the expression for output.

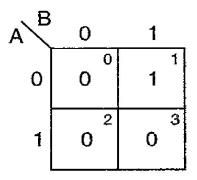

# Example:-

# Map expression $f = \overline{AB} + \overline{AB}$

# Solution:-

The expression minterms is  $F = m_1 + m_2 = m(1, 2)$

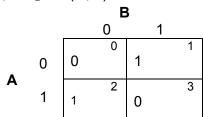

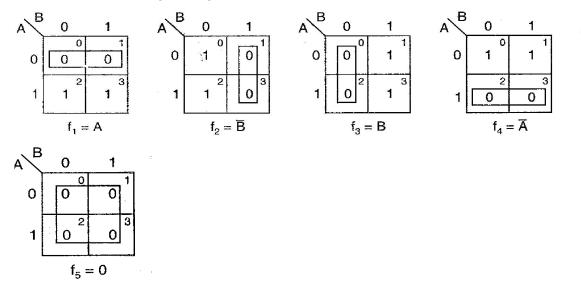

#### Minimization of SOP Expression:-

To minimize a Boolean expression given in the SOP form by using K- map, the adjacent squares having 1s, that is minterms adjacent to each other are combined to form larger squares to eliminate some variables. The possible minterm grouping in a two variable K- map are shown below

- Two minterms, which are adjacent to each other, can be combined to form a bigger square called 2 square or a pair. This eliminates one variable that is not common to both the minterms.

- Two 2-squares adjacent to each other can be combined to form a 4- square. A 4- square eliminates 2 variables. A 4-square is called a quad.

- Consider only those variables which remain constant throughout the square, and ignore the variables which are varying. The non-complemented variable is the variable remaining constant as 1. The complemented variable is the variable remaining constant as a 0 and the variables are written as a product term.

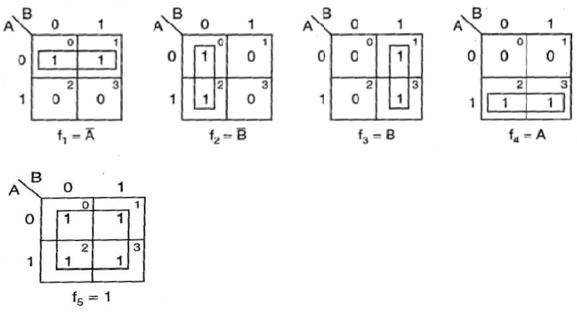

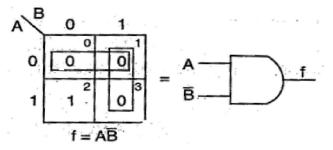

### Example:-

Reduce the expression f= AB + A B + AB using mapping.

#### Solution:-

Expressed in terms of minterms, the given expression is

$F = \overline{A} + B$

#### Mapping of POS Expression:-