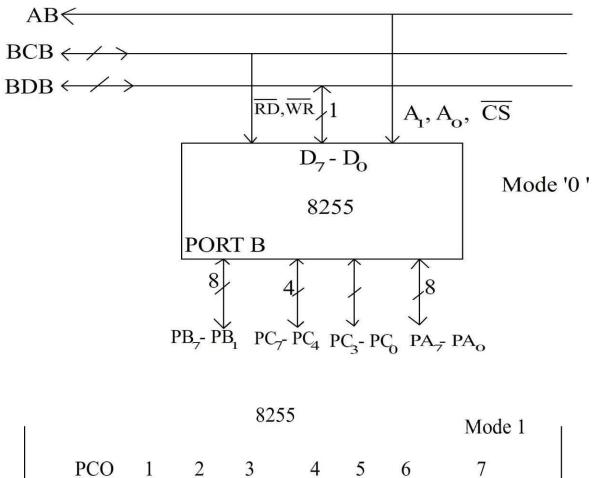

# MICROPROCESSOR AND MICROCONTROLLER

### 4<sup>th</sup> Sem ETC & CSE

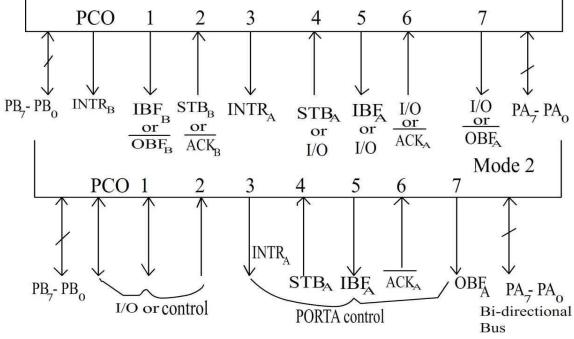

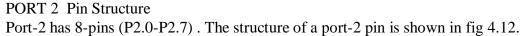

### By

## Suchismita Satpathy

#### **MODULE: 1**

#### 1. INTRODUCTION TO MICROPROCESSOR AND MICROCOMPUTER ARCHITECTURE:

A *microprocessor* is a programmable electronics chip that has computing and decision making capabilities similar to central processing unit of a computer. Any microprocessorbased systems having limited number of resources are called *microcomputers*. Nowadays, microprocessor can be seen in almost all types of electronics devices like mobile phones, printers, washing machines etc. Microprocessors are also used in advanced applications like radars, satellites and flights. Due to the rapid advancements in electronic industry and large scale integration of devices results in a significant cost reduction and increase application of microprocessors and their derivatives.

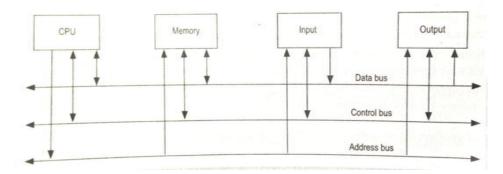

Fig.1 Microprocessor-based system

- **Bit**: A bit is a single binary digit.

- Word: A word refers to the basic data size or bit size that can be processed by the arithmetic and logic unit of the processor. A 16-bit binary number is called a word in a 16-bit processor.

- **Bus**: A bus is a group of wires/lines that carry similar information.

- **System Bus**: The system bus is a group of wires/lines used for communication between the microprocessor and peripherals.

- **Memory Word**: The number of bits that can be stored in a register or memory element is called a memory word.

- Address Bus: It carries the address, which is a unique binary pattern used to identify a memory location or an I/O port. For example, an eight bit address bus has eight lines and thus it can address  $2^8 = 256$  different locations. The locations in hexadecimal format can be written as 00H FFH.

- **Data Bus**: The data bus is used to transfer data between memory and processor or between I/O device and processor. For example, an 8-bit processor will generally have an 8-bit data bus and a 16-bit processor will have 16-bit data bus.

- **Control Bus**: The control bus carry control signals, which consists of signals for selection of memory or I/O device from the given address, direction of data transfer and synchronization of data transfer in case of slow devices.

A typical microprocessor consists of arithmetic and logic unit (ALU) in association with control unit to process the instruction execution. Almost all the microprocessors are based on the principle of store-program concept. In *store-program concept*, programs or instructions are sequentially stored in the memory locations that are to be executed. To do any task using a microprocessor, it is to be programmed by the user. So the programmer must have idea about its internal resources, features and supported instructions. Each microprocessor has a set of instructions, a list which is provided by the microprocessor manufacturer. The instruction set of a microprocessor is provided in two forms: *binary machine code and mnemonics*.

Microprocessor communicates and operates in binary numbers 0 and 1. The set of instructions in the form of binary patterns is called a *machine language* and it is difficult for us to understand. Therefore, the binary patterns are given abbreviated names, called mnemonics, which forms the *assembly language*. The conversion of assembly-level language into binary machine-level language is done by using an application called *assembler*.

#### Technology Used:

The semiconductor manufacturing technologies used for chips are:

- Transistor-Transistor Logic (TTL)

- Emitter Coupled Logic (ECL)

- Complementary Metal-Oxide Semiconductor (CMOS)

### Classification of Microprocessors:

Based on their specification, application and architecture microprocessors are classified.

### Based on size of data bus:

- 4-bit microprocessor

- 8-bit microprocessor

- 16-bit microprocessor

- 32-bit microprocessor

### Based on application:

- General-purpose microprocessor- used in general computer system and can be used by programmer for any application. Examples, 8085 to Intel Pentium.

- Microcontroller- microprocessor with built-in memory and ports and can be programmed for any generic control application. Example, 8051.

- Special-purpose processors- designed to handle special functions required for an application. Examples, digital signal processors and application-specific integrated circuit (ASIC) chips.

#### Based on architecture:

- Reduced Instruction Set Computer (RISC) processors

- Complex Instruction Set Computer (CISC) processors

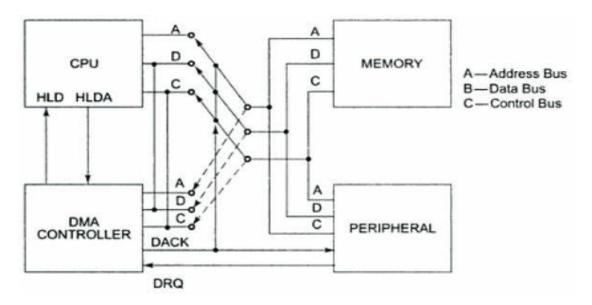

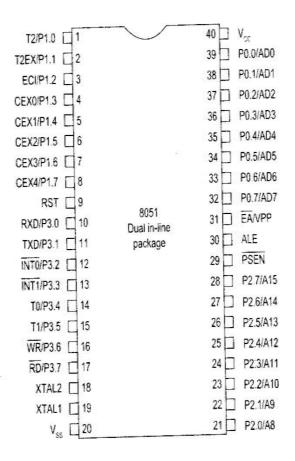

#### 2. 8085 MICROPROCESSOR ARCHITECTURE

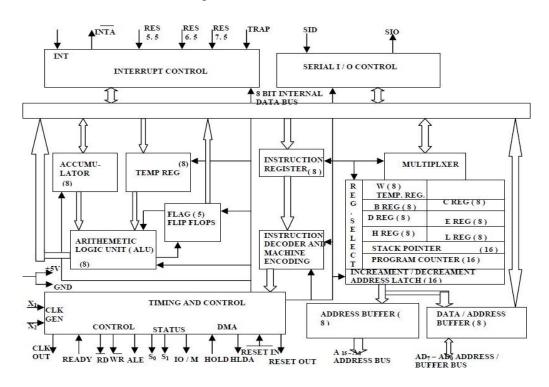

The 8085 microprocessor is an 8-bit processor available as a 40-pin IC package and uses +5 V for power. It can run at a maximum frequency of 3 MHz. Its data bus width is 8-bit and address bus width is 16-bit, thus it can address  $2^{16} = 64$  KB of memory. The internal architecture of 8085 is shown is Fig. 2.

Fig. 2 Internal Architecture of 8085

#### Arithmetic and Logic Unit

The ALU performs the actual numerical and logical operations such as Addition (ADD), Subtraction (SUB), AND, OR etc. It uses data from memory and from Accumulator to perform operations. The results of the arithmetic and logical operations are stored in the accumulator.

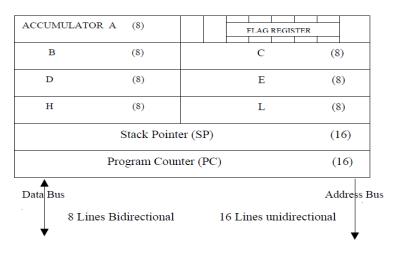

#### Registers

The 8085 includes six registers, one accumulator and one flag register, as shown in Fig. 3. In addition, it has two 16-bit registers: stack pointer and program counter. They are briefly described as follows.

The 8085 has six general-purpose registers to store 8-bit data; these are identified as B, C, D, E, H and L. they can be combined as register pairs - BC, DE and HL to perform some

16-bit operations. The programmer can use these registers to store or copy data into the register by using data copy instructions.

Fig. 3 Register organisation

#### Accumulator

The accumulator is an 8-bit register that is a part of ALU. This register is used to store 8-bit data and to perform arithmetic and logical operations. The result of an operation is stored in the accumulator. The accumulator is also identified as register A.

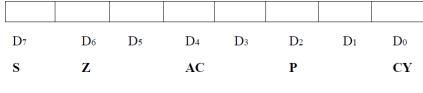

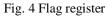

#### Flag register

The ALU includes five flip-flops, which are set or reset after an operation according to data condition of the result in the accumulator and other registers. They are called Zero (Z), Carry (CY), Sign (S), Parity (P) and Auxiliary Carry (AC) flags. Their bit positions in the flag register are shown in Fig. 4. The microprocessor uses these flags to test data conditions.

For example, after an addition of two numbers, if the result in the accumulator is larger than 8-bit, the flip-flop uses to indicate a carry by setting CY flag to 1. When an arithmetic operation results in zero, Z flag is set to 1. The S flag is just a copy of the bit D7 of the accumulator. A negative number has a 1 in bit D7 and a positive number has a 0 in 2's complement representation. The AC flag is set to 1, when a carry result from bit D3 and passes to bit D4. The P flag is set to 1, when the result in accumulator contains even number of 1s.

#### Program Counter (PC)

This 16-bit register deals with sequencing the execution of instructions. This register is a memory pointer. The microprocessor uses this register to sequence the execution of the instructions. The function of the program counter is to point to the memory address from which the next byte is to be fetched. When a byte is being fetched, the program counter is automatically incremented by one to point to the next memory location.

#### Stack Pointer (SP)

The stack pointer is also a 16-bit register, used as a memory pointer. It points to a memory location in R/W memory, called stack. The beginning of the stack is defined by loading 16-bit address in the stack pointer.

#### Instruction Register/Decoder

It is an 8-bit register that temporarily stores the current instruction of a program. Latest instruction sent here from memory prior to execution. Decoder then takes instruction and decodes or interprets the instruction. Decoded instruction then passed to next stage.

#### Control Unit

Generates signals on data bus, address bus and control bus within microprocessor to carry out the instruction, which has been decoded. Typical buses and their timing are described as follows:

- Data Bus: Data bus carries data in binary form between microprocessor and other external units such as memory. It is used to transmit data i.e. information, results of arithmetic etc between memory and the microprocessor. Data bus is bidirectional in nature. The data bus width of 8085 microprocessor is 8-bit i.e. 2<sup>8</sup> combination of binary digits and are typically identified as D0 D7. Thus size of the data bus determines what arithmetic can be done. If only 8-bit wide then largest number is 11111111 (255 in decimal). Therefore, larger numbers have to be broken down into chunks of 255. This slows microprocessor.

- Address Bus: The address bus carries addresses and is one way bus from microprocessor to the memory or other devices. 8085 microprocessor contain 16-bit address bus and are generally identified as A0 A15. The higher order address lines (A8 A15) are unidirectional and the lower order lines (A0 A7) are multiplexed (time-shared) with the eight data bits (D0 D7) and hence, they are bidirectional.

- *Control Bus*: Control bus are various lines which have specific functions for coordinating and controlling microprocessor operations. The control bus carries control signals partly unidirectional and partly bidirectional. The following control and status signals are used by 8085 processor:

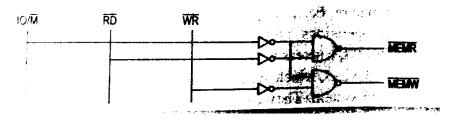

- I. ALE (output): Address Latch Enable is a pulse that is provided when an address appears on the AD0 AD7 lines, after which it becomes 0.

- II. RD (active low output): The Read signal indicates that data are being read from the selected I/O or memory device and that they are available on the data bus.

- III. WR (active low output): The Write signal indicates that data on the data bus are to be written into a selected memory or I/O location.

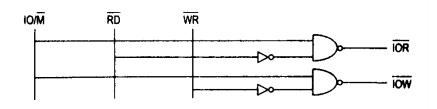

- IV. IO/M (output): It is a signal that distinguished between a memory operation and an I/O operation. When  $IO/\overline{M} = 0$  it is a memory operation and  $IO/\overline{M} = 1$  it is an I/O operation.

- V. S1 and S0 (output): These are status signals used to specify the type of operation being performed; they are listed in Table 1.

| S1 | <b>S</b> 0 | States |

|----|------------|--------|

| 0  | 0          | Halt   |

| 0  | 1          | Write  |

| 1  | 0          | Read   |

| 1  | 1          | Fetch  |

Table 1 Status signals and associated operations

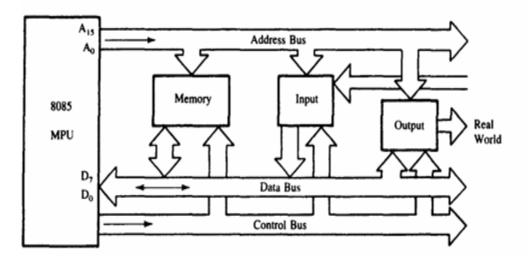

The schematic representation of the 8085 bus structure is as shown in Fig. 5. The microprocessor performs primarily four operations:

- I. Memory Read: Reads data (or instruction) from memory.

- II. Memory Write: Writes data (or instruction) into memory.

- III. I/O Read: Accepts data from input device.

- IV. I/O Write: Sends data to output device.

The 8085 processor performs these functions using address bus, data bus and control bus as shown in Fig. 5.

Fig. 5 The 8085 bus structure

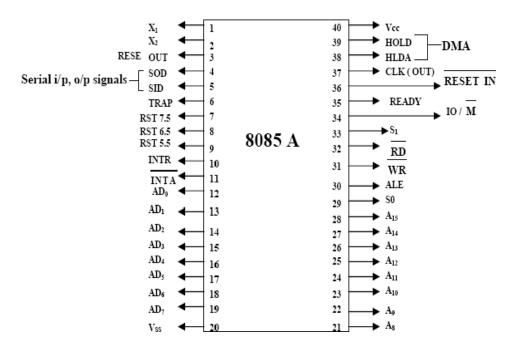

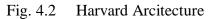

#### 3. 8085 PIN DESCRIPTION

#### Properties:

- It is a 8-bit microprocessor

- Manufactured with N-MOS technology

- 40 pin IC package

- It has 16-bit address bus and thus has  $2^{16} = 64$  KB addressing capability.

- Operate with 3 MHz single-phase clock

- +5 V single power supply

The logic pin layout and signal groups of the 8085nmicroprocessor are shown in Fig. 6. All the signals are classified into six groups:

- Address bus

- Data bus

- Control & status signals

- Power supply and frequency signals

- Externally initiated signals

- Serial I/O signals

Fig. 6 8085 microprocessor pin layout and signal groups

Address and Data Buses:

- A8 A15 (output, 3-state): Most significant eight bits of memory addresses and the eight bits of the I/O addresses. These lines enter into tri-state high impedance state during HOLD and HALT modes.

- AD0 AD7 (input/output, 3-state): Lower significant bits of memory addresses and the eight bits of the I/O addresses during first clock cycle. Behaves as data bus

during third and fourth clock cycle. These lines enter into tri-state high impedance state during HOLD and HALT modes.

Control & Status Signals:

- ALE: Address latch enable

- $\overline{\text{RD}}$ : Read control signal.

- WR : Write control signal.

- IO/M, S1 and S0 : Status signals.

Power Supply & Clock Frequency:

- Vcc: +5 V power supply

- Vss: Ground reference

- X1, X2: A crystal having frequency of 6 MHz is connected at these two pins

- CLK: Clock output

Externally Initiated and Interrupt Signals:

- **RESET** IN: When the signal on this pin is low, the PC is set to 0, the buses are tristated and the processor is reset.

- RESET OUT: This signal indicates that the processor is being reset. The signal can be used to reset other devices.

- READY: When this signal is low, the processor waits for an integral number of clock cycles until it goes high.

- HOLD: This signal indicates that a peripheral like DMA (direct memory access) controller is requesting the use of address and data bus.

- HLDA: This signal acknowledges the HOLD request.

- INTR: Interrupt request is a general-purpose interrupt.

- INTA : This is used to acknowledge an interrupt.

- RST 7.5, RST 6.5, RST 5,5 restart interrupt: These are vectored interrupts and have highest priority than INTR interrupt.

- TRAP: This is a non-maskable interrupt and has the highest priority.

Serial I/O Signals:

- SID: Serial input signal. Bit on this line is loaded to D7 bit of register A using RIM instruction.

- SOD: Serial output signal. Output SOD is set or reset by using SIM instruction.

•

#### 4. INSTRUCTION SET AND EXECUTION IN 8085

Based on the design of the ALU and decoding unit, the microprocessor manufacturer provides instruction set for every microprocessor. The instruction set consists of both machine code and mnemonics.

An instruction is a binary pattern designed inside a microprocessor to perform a specific function. The entire group of instructions that a microprocessor supports is called instruction set. Microprocessor instructions can be classified based on the parameters such functionality, length and operand addressing.

Classification based on functionality:

- I. Data transfer operations: This group of instructions copies data from source to destination. The content of the source is not altered.

- II. Arithmetic operations: Instructions of this group perform operations like addition, subtraction, increment & decrement. One of the data used in arithmetic operation is stored in accumulator and the result is also stored in accumulator.

- III. Logical operations: Logical operations include AND, OR, EXOR, NOT. The operations like AND, OR and EXOR uses two operands, one is stored in accumulator and other can be any register or memory location. The result is stored in accumulator. NOT operation requires single operand, which is stored in accumulator.

- IV. Branching operations: Instructions in this group can be used to transfer program sequence from one memory location to another either conditionally or unconditionally.

- V. Machine control operations: Instruction in this group control execution of other instructions and control operations like interrupt, halt etc.

Classification based on length:

- I. One-byte instructions: Instruction having one byte in machine code. Examples are depicted in Table 2.

- I. Two-byte instructions: Instruction having two byte in machine code. Examples are depicted in Table 3

- II. Three-byte instructions: Instruction having three byte in machine code. Examples are depicted in Table 4.

| Opcode | Operand | Machine code/Hex code |

|--------|---------|-----------------------|

| MOV    | A, B    | 78                    |

| ADD    | М       | 86                    |

|        |         | 1 7                   |                  |

|--------|---------|-----------------------|------------------|

| Opcode | Operand | Machine code/Hex code | Byte description |

| MVI    | A, 7FH  | 3E                    | First byte       |

|        |         | 7F                    | Second byte      |

| ADI    | 0FH     | C6                    | First byte       |

|        |         | OF                    | Second byte      |

Table 3 Examples of two byte instructions

Table 4 Examples of three byte instructions

| Opcode | Operand | Machine code/Hex code | Byte description |

|--------|---------|-----------------------|------------------|

| JMP    | 9050H   | C3                    | First byte       |

|        |         | 50                    | Second byte      |

|        |         | 90                    | Third byte       |

| LDA    | 8850H   | 3A                    | First byte       |

|        |         | 50                    | Second byte      |

|        |         | 88                    | Third byte       |

Addressing Modes in Instructions:

The process of specifying the data to be operated on by the instruction is called addressing. The various formats for specifying operands are called addressing modes. The 8085 has the following five types of addressing:

- I. Immediate addressing

- II. Memory direct addressing

- III. Register direct addressing

- IV. Indirect addressing

- V. Implicit addressing

Immediate Addressing:

In this mode, the operand given in the instruction - a byte or word – transfers to the destination register or memory location.

Ex: MVI A, 9AH

- The operand is a part of the instruction.

- The operand is stored in the register mentioned in the instruction.

Memory Direct Addressing:

Memory direct addressing moves a byte or word between a memory location and register. The memory location address is given in the instruction.

#### Ex: LDA 850FH

This instruction is used to load the content of memory address 850FH in the accumulator.

Register Direct Addressing:

Register direct addressing transfer a copy of a byte or word from source register to destination register.

Ex: MOV B, C

It copies the content of register C to register B.

Indirect Addressing:

Indirect addressing transfers a byte or word between a register and a memory location.

Ex: MOV A, M

Here the data is in the memory location pointed to by the contents of HL pair. The data is moved to the accumulator.

Implicit Addressing

In this addressing mode the data itself specifies the data to be operated upon.

Ex: CMA

The instruction complements the content of the accumulator. No specific data or operand is mentioned in the instruction.

#### 5. INSTRUCTION SET OF 8085

Data Transfer Instructions:

| Opcode           | Operand                                             | Description                                                                                                                                                                                                                                                                                              |

|------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Copy from<br>MOV | n source to destination<br>Rd, Rs<br>M, Rs<br>Rd, M | This instruction copies the contents of the source<br>register into the destination register; the contents of<br>the source register are not altered. If one of the operands is a<br>memory location, its location is specified by the contents of<br>the HL registers.<br>Example: MOV B, C or MOV B, M |

| Move im<br>MVI   | mediate 8-bit<br>Rd, data<br>M, data                | The 8-bit data is stored in the destination register or<br>memory. If the operand is a memory location, its location is<br>specified by the contents of the HL registers.<br>Example: MVI B, 57 or MVI M, 57                                                                                             |

| Load acer<br>LDA | umulator<br>16-bit address                          | The contents of a memory location, specified by a<br>16-bit address in the operand, are copied to the accumulator.<br>The contents of the source are not altered.<br>Example: LDA 2034 or LDA XYZ                                                                                                        |

| Load ace<br>LDAX | umulator indirect<br>B/D Reg. pair                  | The contents of the designated register pair point to a memory<br>location. This instruction copies the contents of that memory<br>location into the accumulator. The contents of either the<br>register pair or the memory location are not altered.<br>Example: LDAX B                                 |

| Load reg<br>LXI  | ister pair immediate<br>Reg. pair, 16-bit data      | The instruction loads 16-bit data in the register pair<br>designated in the operand.<br>Example: LXI H, 2034                                                                                                                                                                                             |

| Load H a<br>LHLD | und L registers direct<br>16-bit address            | The instruction copies the contents of the memory location<br>pointed out by the 16-bit address into register L and copies<br>the contents of the next memory location into register H. The<br>contents of source memory locations are not altered.<br>Example: LHLD 2040                                |

| Store accu         | mulator direct                        |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STA                | 16-bit address                        | The contents of the accumulator are copied into the memory<br>location specified by the operand. This is a 3-byte<br>instruction, the second byte specifies the low-order address<br>and the third byte specifies the high-order address.<br>Example: STA 4350 or STA XYZ                                                                                                                                                                   |

| Store accu<br>STAX | mulator indirect<br>Reg. pair         | The contents of the accumulator are copied into the memory<br>location specified by the contents of the operand (register<br>pair). The contents of the accumulator are not altered.<br>Example: STAX B                                                                                                                                                                                                                                     |

|                    | d L registers direct                  |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SHLD               | 16-bit address                        | The contents of register L are stored into the memory location<br>specified by the 16-bit address in the operand and the contents<br>of H register are stored into the next memory location by<br>incrementing the operand. The contents of registers HL are<br>not altered. This is a 3-byte instruction, the second byte<br>specifies the low-order address and the third byte specifies the<br>high-order address.<br>Example: SHLD 2470 |

| Exchange<br>XCHG   | H and L with D and E<br>none          | The contents of register H are exchanged with the contents of register D, and the contents of register L are exchanged with the contents of register E. Example: XCHG                                                                                                                                                                                                                                                                       |

| Copy H ar<br>SPHL  | nd L registers to the stack p<br>none | The instruction loads the contents of the H and L registers<br>into the stack pointer register, the contents of the H register<br>provide the high-order address and the contents of the L<br>register provide the low-order address. The contents of the H<br>and L registers are not altered.<br>Example: SPHL                                                                                                                            |

| Exchange<br>XTHL   | H and L with top of stack none        | The contents of the L register are exchanged with the stack<br>location pointed out by the contents of the stack pointer<br>register. The contents of the H register are exchanged with<br>the next stack location (SP+1); however, the contents of the<br>stack pointer register are not altered.<br>Example: XTHL                                                                                                                         |

|                  | ter pair onto stack                              |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PUSH             | Reg. pair                                        | The contents of the register pair designated in the operand are<br>copied onto the stack in the following sequence. The stack<br>pointer register is decremented and the contents of the high-<br>order register (B, D, H, A) are copied into that location. The<br>stack pointer register is decremented again and the contents of<br>the low-order register (C, E, L, flags) are copied to that<br>location.<br>Example: PUSH B or PUSH A |

|                  | ack to register pair                             |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| РОР              | Reg. pair                                        | The contents of the memory location pointed out by the stack<br>pointer register are copied to the low-order register (C, E, L,<br>status flags) of the operand. The stack pointer is incremented<br>by 1 and the contents of that memory location are copied to<br>the high-order register (B, D, H, A) of the operand. The stack<br>pointer register is again incremented by 1.<br>Example: POP H or POP A                                |

| Output da<br>OUT | ta from accumulator to a p<br>8-bit port address | port with 8-bit address<br>The contents of the accumulator are copied into the I/O port<br>specified by the operand.<br>Example: OUT 87                                                                                                                                                                                                                                                                                                     |

| Input data<br>IN | to accumulator from a po<br>8-bit port address   | ort with 8-bit address<br>The contents of the input port designated in the operand are<br>read and loaded into the accumulator.<br>Example: IN 82                                                                                                                                                                                                                                                                                           |

| Arithmetic       | Instructions:                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Opcode           | Operand                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Add regis        | ter or memory to accumula                        | tor                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ADD              | R<br>M                                           | The contents of the operand (register or memory) are<br>added to the contents of the accumulator and the result is<br>stored in the accumulator. If the operand is a memory<br>location, its location is specified by the contents of the HL<br>registers. All flags are modified to reflect the result of the<br>addition.<br>Example: ADD B or ADD M                                                                                      |

| Add regis        | ter to accumulator with car                      | ту                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ADC              | R<br>M                                           | The contents of the operand (register or memory) and<br>the Carry flag are added to the contents of the accumulator<br>and the result is stored in the accumulator. If the operand is a<br>memory location, its location is specified by the contents of<br>the HL registers. All flags are modified to reflect the result of<br>the addition.<br>Example: ADC B or ADC M                                                                   |

| Add imme<br>ADI  | ediate to accumulator<br>8-bit data              | The 8-bit data (operand) is added to the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the addition. Example: ADI 45                                                                                                                                                                                                                                             |

| Add imme         | ediate to accumulator with                       | carry                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ACI              | 8-bit data                                       | The 8-bit data (operand) and the Carry flag are added to the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the addition.<br>Example: ACI 45                                                                                                                                                                                                                      |

|                  | ter pair to H and L register                     |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DAD              | Reg. pair                                        | The 16-bit contents of the specified register pair are added to<br>the contents of the HL register and the sum is stored in the<br>HL register. The contents of the source register pair are not<br>altered. If the result is larger than 16 bits, the CY flag is set.<br>No other flags are affected.<br>Example: DAD H                                                                                                                    |

Subtract register or memory from accumulator

| SUB R<br>M                                           | The contents of the operand (register or memory ) are<br>subtracted from the contents of the accumulator, and the<br>result is stored in the accumulator. If the operand is a<br>memory location, its location is specified by the contents of<br>the HL registers. All flags are modified to reflect the result of<br>the subtraction.<br>Example: SUB B or SUB M                                 |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Subtract source and borrow from act<br>SBB R<br>M    | cumulator<br>The contents of the operand (register or memory ) and<br>the Borrow flag are subtracted from the contents of the<br>accumulator and the result is placed in the accumulator. If<br>the operand is a memory location, its location is specified by<br>the contents of the HL registers. All flags are modified to<br>reflect the result of the subtraction.<br>Example: SBB B or SBB M |

| Subtract immediate from accumulate<br>SUI 8-bit data | or<br>The 8-bit data (operand) is subtracted from the contents of the<br>accumulator and the result is stored in the accumulator. All<br>flags are modified to reflect the result of the subtraction.<br>Example: SUI 45                                                                                                                                                                           |

| Subtract immediate from accumulate<br>SBI 8-bit data | or with borrow<br>The 8-bit data (operand) and the Borrow flag are subtracted<br>from the contents of the accumulator and the result is stored<br>in the accumulator. All flags are modified to reflect the result<br>of the subtracion.<br>Example: SBI 45                                                                                                                                        |

| Increment register or memory by 1<br>INR R<br>M      | The contents of the designated register or memory) are<br>incremented by 1 and the result is stored in the same place. If<br>the operand is a memory location, its location is specified by<br>the contents of the HL registers.<br>Example: INR B or INR M                                                                                                                                        |

| Increment register pair by 1<br>INX R                | The contents of the designated register pair are incremented<br>by 1 and the result is stored in the same place.<br>Example: INX H                                                                                                                                                                                                                                                                 |

| Decrement register or memory by 1<br>DCR R<br>M | The contents of the designated register or memory are<br>decremented by 1 and the result is stored in the same place. If<br>the operand is a memory location, its location is specified by<br>the contents of the HL registers.<br>Example: DCR B or DCR M                                                                                                    |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Decrement register pair by 1<br>DCX R           | The contents of the designated register pair are decremented<br>by 1 and the result is stored in the same place.<br>Example: DCX H                                                                                                                                                                                                                            |

| Decimal adjust accumulator<br>DAA none          | The contents of the accumulator are changed from a binary<br>value to two 4-bit binary coded decimal (BCD) digits. This is<br>the only instruction that uses the auxiliary flag to perform the<br>binary to BCD conversion, and the conversion procedure is<br>described below. S, Z, AC, P, CY flags are altered to reflect<br>the results of the operation. |

|                                                 | If the value of the low-order 4-bits in the accumulator is greater than 9 or if AC flag is set, the instruction adds 6 to the low-order four bits.                                                                                                                                                                                                            |

|                                                 | If the value of the high-order 4-bits in the accumulator is greater than 9 or if the Carry flag is set, the instruction adds 6 to the high-order four bits.                                                                                                                                                                                                   |

|                                                 | Example: DAA                                                                                                                                                                                                                                                                                                                                                  |

#### **BRANCHING INSTRUCTIONS**

| Opcode          | Operand                        | Description                                                                                                                                   |

|-----------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Jump une<br>JMP | onditionally<br>16-bit address | The program sequence is transferred to the memory location specified by the 16-bit address given in the operand. Example: JMP 2034 or JMP XYZ |

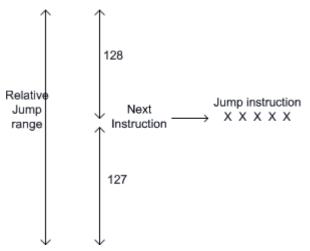

Jump conditionally

Operand: 16-bit address

The program sequence is transferred to the memory location specified by the 16-bit address given in the operand based on the specified flag of the PSW as described below. Example: JZ 2034 or JZ XYZ

| Opcode | Description         | Flag Status      |

|--------|---------------------|------------------|

| JC     | Jump on Carry       | CY = 1           |

| JNC    | Jump on no Carry    | CY = 0           |

| JP     | Jump on positive    | S = 0            |

| JM     | Jump on minus       | S = 1            |

| JZ     | Jump on zero        | Z = 1            |

| JNZ    | Jump on no zero     | $\mathbf{Z} = 0$ |

| JPE    | Jump on parity even | $\mathbf{P} = 1$ |

| JPO    | Jump on parity odd  | $\mathbf{P} = 0$ |

Unconditional subroutine call CALL 16-bit address

The program sequence is transferred to the memory location specified by the 16-bit address given in the operand. Before the transfer, the address of the next instruction after CALL (the contents of the program counter) is pushed onto the stack. Example: CALL 2034 or CALL XYZ

Call conditionally

Operand: 16-bit address

The program sequence is transferred to the memory location specified by the 16-bit address given in the operand based on the specified flag of the PSW as described below. Before the transfer, the address of the next instruction after the call (the contents of the program counter) is pushed onto the stack. Example: CZ 2034 or CZ XYZ

| Opcode | Description         | Flag Status      |

|--------|---------------------|------------------|

| CC     | Call on Carry       | CY = 1           |

| CNC    | Call on no Carry    | CY = 0           |

| CP     | Call on positive    | S = 0            |

| CM     | Call on minus       | S = 1            |

| CZ     | Call on zero        | Z = 1            |

| CNZ    | Call on no zero     | $\mathbf{Z} = 0$ |

| CPE    | Call on parity even | $\mathbf{P} = 1$ |

| CPO    | Call on parity odd  | $\mathbf{P} = 0$ |

Return from subroutine unconditionally

RET none

The program sequence is transferred from the subroutine to the calling program. The two bytes from the top of the stack are copied into the program counter, and program execution begins at the new address. Example: RET

Return from subroutine conditionally

Operand: none

The program sequence is transferred from the subroutine to the calling program based on the specified flag of the PSW as described below. The two bytes from the top of the stack are copied into the program counter, and program execution begins at the new address. Example: RZ

| Opcode Description        | Flag Status      |

|---------------------------|------------------|

| RC Return on Carry        | CY = 1           |

| RNC Return on no Carry    | CY = 0           |

| RP Return on positive     | S = 0            |

| RM Return on minus        | S = 1            |

| RZ Return on zero         | Z = 1            |

| RNZ Return on no zero     | $\mathbf{Z} = 0$ |

| RPE Return on parity even | $\mathbf{P} = 1$ |

| RPO Return on parity odd  | $\mathbf{P} = 0$ |

Load program counter with HL contents PCHL none The

The contents of registers H and L are copied into the program counter. The contents of H are placed as the high-order byte and the contents of L as the low-order byte. Example: PCHL

Restart RST 0-7

The RST instruction is equivalent to a 1-byte call instruction to one of eight memory locations depending upon the number. The instructions are generally used in conjunction with interrupts and inserted using external hardware. However these can be used as software instructions in a program to transfer program execution to one of the eight locations. The addresses are:

| Instruction | Restart Address |

|-------------|-----------------|

| RST 0       | 0000H           |

| RST 1       | 0008H           |

| RST 2       | 0010H           |

| RST 3       | 0018H           |

| RST 4       | 0020H           |

| RST 5       | 0028H           |

| RST 6       | 0030H           |

| RST 7       | 0038H           |

The 8085 has four additional interrupts and these interrupts generate RST instructions internally and thus do not require any external hardware. These instructions and their Restart addresses are:

| Interrupt      | Restart Address |

|----------------|-----------------|

| TRAP           | 0024H           |

| RST 5.5        | 002CH           |

| <b>RST 6.5</b> | 0034H           |

| RST 7.5        | 003CH           |

#### LOGICAL INSTRUCTIONS

| Opcode           | Operand                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Compare<br>CMP   | register or memory with a<br>R<br>M   | ccumulator<br>The contents of the operand (register or memory) are<br>compared with the contents of the accumulator. Both<br>contents are preserved . The result of the comparison is<br>shown by setting the flags of the PSW as follows:<br>if (A) < (reg/mem): carry flag is set, $s=1$<br>if (A) = (reg/mem): zero flag is set, $s=0$<br>if (A) > (reg/mem): carry and zero flags are reset, $s=0$<br>Example: CMP B or CMP M |

| Compare          | immediate with accumulat              | tor                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CPI              | 8-bit data                            | The second byte (8-bit data) is compared with the contents of<br>the accumulator. The values being compared remain<br>unchanged. The result of the comparison is shown by setting<br>the flags of the PSW as follows:<br>if (A) < data: carry flag is set, s=1<br>if (A) = data: zero flag is set, s=0<br>if (A) > data: carry and zero flags are reset, s=0<br>Example: CPI 89                                                   |

| Logical A<br>ANA | ND register or memory w<br>R<br>M     | ith accumulator<br>The contents of the accumulator are logically ANDed with<br>the contents of the operand (register or memory), and the<br>result is placed in the accumulator. If the operand is a<br>memory location, its address is specified by the contents of<br>HL registers. S, Z, P are modified to reflect the result of the<br>operation. CY is reset. AC is set.<br>Example: ANA B or ANA M                          |

| Logical A<br>ANI | ND immediate with accum<br>8-bit data | nulator<br>The contents of the accumulator are logically ANDed with the<br>8-bit data (operand) and the result is placed in the<br>accumulator. S, Z, P are modified to reflect the result of the<br>operation. CY is reset. AC is set.<br>Example: ANI 86                                                                                                                                                                        |

| Exclusive<br>XRA  | OR register or memory w<br>R<br>M     | ith accumulator<br>The contents of the accumulator are Exclusive ORed with<br>the contents of the operand (register or memory), and the<br>result is placed in the accumulator. If the operand is a<br>memory location, its address is specified by the contents of<br>HL registers. S, Z, P are modified to reflect the result of the<br>operation. CY and AC are reset.<br>Example: XRA B or XRA M |

|-------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Exclusive<br>XRI  | OR immediate with accum<br>8-bit data | nulator<br>The contents of the accumulator are Exclusive ORed with the<br>8-bit data (operand) and the result is placed in the<br>accumulator. S, Z, P are modified to reflect the result of the<br>operation. CY and AC are reset.<br>Example: XRI 86                                                                                                                                               |

| Logical O<br>ORA  | R register or memory with<br>R<br>M   | accumulaotr<br>The contents of the accumulator are logically ORed with<br>the contents of the operand (register or memory), and the<br>result is placed in the accumulator. If the operand is a<br>memory location, its address is specified by the contents of<br>HL registers. S, Z, P are modified to reflect the result of the<br>operation. CY and AC are reset.<br>Example: ORA B or ORA M     |

| I                 | D '                                   | 1.4                                                                                                                                                                                                                                                                                                                                                                                                  |

| ORI               | R immediate with accumu<br>8-bit data | The contents of the accumulator are logically ORed with the<br>8-bit data (operand) and the result is placed in the<br>accumulator. S, Z, P are modified to reflect the result of the<br>operation. CY and AC are reset.<br>Example: ORI 86                                                                                                                                                          |

| Rotate acc<br>RLC | eumulator left<br>none                | Each binary bit of the accumulator is rotated left by one position. Bit D7 is placed in the position of D0 as well as in the Carry flag. CY is modified according to bit D7. S, Z, P, AC are not affected.<br>Example: RLC                                                                                                                                                                           |

| Rotate acc<br>RRC | cumulator right<br>none               | Each binary bit of the accumulator is rotated right by one<br>position. Bit D <sub>0</sub> is placed in the position of D <sub>7</sub> as well as in<br>the Carry flag. CY is modified according to bit D <sub>0</sub> . S, Z, P,<br>AC are not affected.<br>Example: RRC                                                                                                                            |

| Rotate acc<br>RAL | rumulator left through carr<br>none | Each binary bit of the accumulator is rotated left by one<br>position through the Carry flag. Bit D7 is placed in the Carry<br>flag, and the Carry flag is placed in the least significant<br>position D0. CY is modified according to bit D7. S, Z, P, AC<br>are not affected.<br>Example: RAL                                       |

|-------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rotate acc<br>RAR | umulator right through car<br>none  | Each binary bit of the accumulator is rotated right by one<br>position through the Carry flag. Bit D <sub>0</sub> is placed in the Carry<br>flag, and the Carry flag is placed in the most significant<br>position D <sub>7</sub> . CY is modified according to bit D <sub>0</sub> . S, Z, P, AC<br>are not affected.<br>Example: RAR |

| Complem<br>CMA    | ent accumulator<br>none             | The contents of the accumulator are complemented. No flags are affected.                                                                                                                                                                                                                                                              |

|                   |                                     | Example: CMA                                                                                                                                                                                                                                                                                                                          |

| Complem<br>CMC    | ent carry<br>none                   | The Carry flag is complemented. No other flags are affected.<br>Example: CMC                                                                                                                                                                                                                                                          |

| Set Carry<br>STC  | none                                | The Carry flag is set to 1. No other flags are affected.<br>Example: STC                                                                                                                                                                                                                                                              |

| CONTR             | OL INSTRUCTIONS                     |                                                                                                                                                                                                                                                                                                                                       |

| Opcode            | Operand                             | Description                                                                                                                                                                                                                                                                                                                           |

| No opera<br>NOP   | tion<br>none                        | No operation is performed. The instruction is fetched and decoded. However no operation is executed. Example: NOP                                                                                                                                                                                                                     |

| Halt and<br>HLT   | enter wait state<br>none            | The CPU finishes executing the current instruction and halts<br>any further execution. An interrupt or reset is necessary to<br>exit from the halt state.<br>Example: HLT                                                                                                                                                             |

| Disable i<br>DI   | nterrupts<br>none                   | The interrupt enable flip-flop is reset and all the interrupts except the TRAP are disabled. No flags are affected. Example: DI                                                                                                                                                                                                       |

| Enable in<br>EI   | iterrupts<br>none                   | The interrupt enable flip-flop is set and all interrupts are<br>enabled. No flags are affected. After a system reset or the<br>acknowledgement of an interrupt, the interrupt enable flip-<br>flop is reset, thus disabling the interrupts. This instruction is<br>necessary to reenable the interrupts (except TRAP).<br>Example: EI |

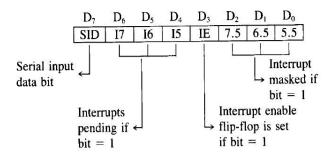

Read interrupt mask RIM none

This is a multipurpose instruction used to read the status of interrupts 7.5, 6.5, 5.5 and read serial data input bit. The instruction loads eight bits in the accumulator with the following interpretations. Example: RIM

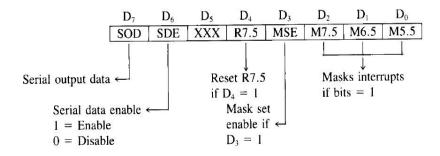

Set interrupt mask SIM none

This is a multipurpose instruction and used to implement the 8085 interrupts 7.5, 6.5, 5.5, and serial data output. The instruction interprets the accumulator contents as follows. Example: SIM

- □ SOD—Serial Output Data: Bit  $D_7$  of the accumulator is latched into the SOD output line and made available to a serial peripheral if bit  $D_6 = 1$ .

- $\Box$  SDE Serial Data Enable: If this bit = 1, it enables the serial output. To implement serial output, this bit needs to be enabled.

- □ XXX—Don't Care

- □ R7.5—Reset RST 7.5: If this bit = 1, RST 7.5 flip-flop is reset. This is an additional control to reset RST 7.5.

- $\square$  MSE Mask Set Enable: If this bit is high, it enables the functions of bits D<sub>2</sub>, D<sub>1</sub>, D<sub>0</sub>. This is a master control over all the interrupt masking bits. If this bit is low, bits D<sub>2</sub>, D<sub>1</sub>, and D<sub>0</sub> do not have any effect on the masks.

- $\square$  M7.5—D<sub>2</sub> = 0, RST 7.5 is enabled.

- = 1, RST 7.5 is masked or disabled.

- $\square$  M6.5—D<sub>1</sub> = 0, RST 6.5 is enabled.

- = 1, RST 6.5 is masked or disabled.

- $\square$  M5.5—D<sub>0</sub> = 0, RST 5.5 is enabled.

= 1, RST 5.5 is masked or disabled.

### 6. INSTRUCTION EXECUTION AND TIMING DIAGRAM:

Each instruction in 8085 microprocessor consists of two part- operation code (opcode) and operand. The opcode is a command such as ADD and the operand is an object to be operated on, such as a byte or the content of a register.

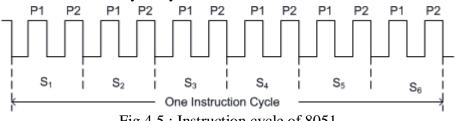

Instruction Cycle: The time taken by the processor to complete the execution of an instruction. An instruction cycle consists of one to six machine cycles.

Machine Cycle: The time required to complete one operation; accessing either the memory or I/O device. A machine cycle consists of three to six T-states.

T-State: Time corresponding to one clock period. It is the basic unit to calculate execution of instructions or programs in a processor.

To execute a program, 8085 performs various operations as:

- Opcode fetch

- Operand fetch

- Memory read/write

- I/O read/write

External communication functions are:

- Memory read/write

- I/O read/write

- Interrupt request acknowledge

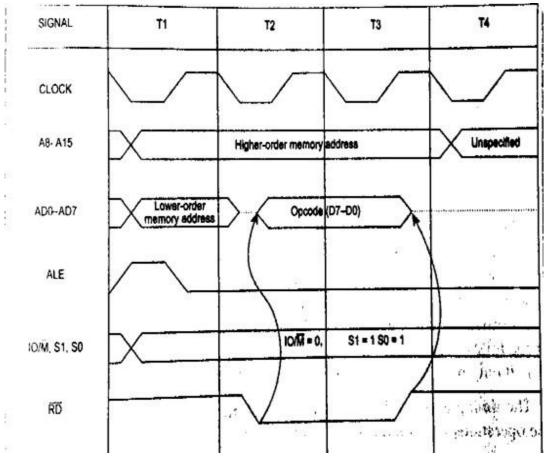

Opcode Fetch Machine Cycle:

It is the first step in the execution of any instruction. The timing diagram of this cycle is given in Fig. 7.

The following points explain the various operations that take place and the signals that are changed during the execution of opcode fetch machine cycle:

T1 clock cycle

- i. The content of PC is placed in the address bus; AD0 AD7 lines contains lower bit address and A8 A15 contains higher bit address.

- ii. IO/M signal is low indicating that a memory location is being accessed. S1 and S0 also changed to the levels as indicated in Table 1.

- iii. ALE is high, indicates that multiplexed AD0 AD7 act as lower order bus.

T2 clock cycle

- i. Multiplexed address bus is now changed to data bus.

- ii. The RD signal is made low by the processor. This signal makes the memory device load the data bus with the contents of the location addressed by the processor.

T3 clock cycle

- i. The opcode available on the data bus is read by the processor and moved to the instruction register.

- ii. The  $\overline{RD}$  signal is deactivated by making it logic 1.

T4 clock cycle

i. The processor decode the instruction in the instruction register and generate the necessary control signals to execute the instruction. Based on the instruction further operations such as fetching, writing into memory etc takes place.

Fig. 7 Timing diagram for opcode fetch cycle

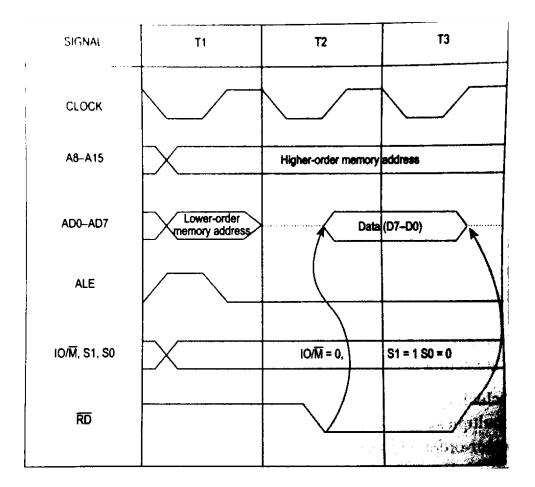

Memory Read Machine Cycle:

The memory read cycle is executed by the processor to read a data byte from memory. The machine cycle is exactly same to opcode fetch except: a) It has three T-states b) The S0 signal is set to 0. The timing diagram of this cycle is given in Fig. 8.

Fig. 8 Timing diagram for memory read machine cycle

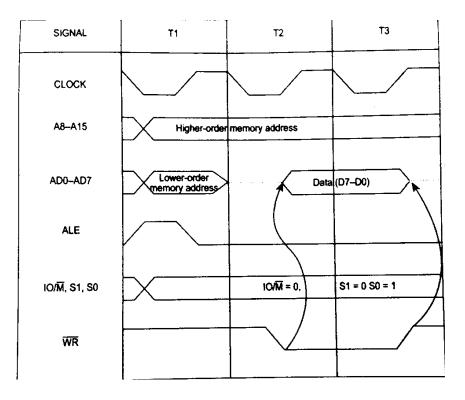

Memory Write Machine Cycle:

The memory write cycle is executed by the processor to write a data byte in a memory location. The processor takes three T-states and  $\overline{WR}$  signal is made low. The timing diagram of this cycle is given in Fig. 9.

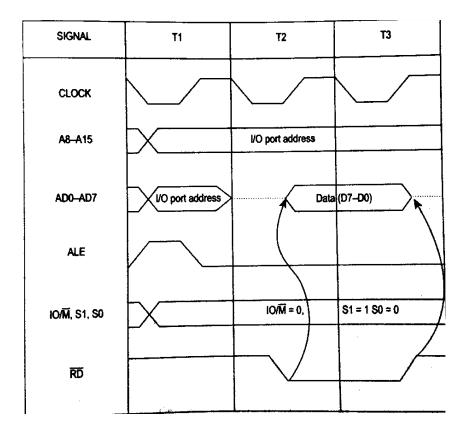

I/O Read Cycle:

The I/O read cycle is executed by the processor to read a data byte from I/O port or from peripheral, which is I/O mapped in the system. The 8-bit port address is placed both in the lower and higher order address bus. The processor takes three T-states to execute this machine cycle. The timing diagram of this cycle is given in Fig. 10.

Fig. 9 Timing diagram for memory write machine cycle

Fig. 10 Timing diagram I/O read machine cycle

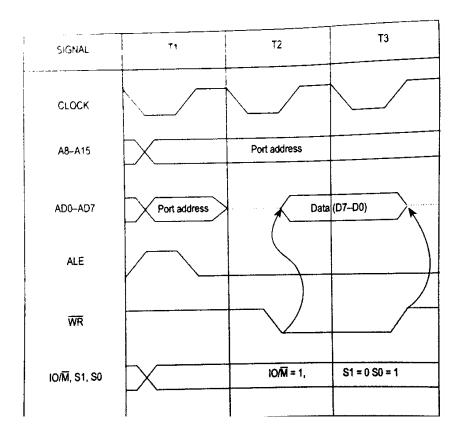

#### I/O Write Cycle:

The I/O write cycle is executed by the processor to write a data byte to I/O port or to a peripheral, which is I/O mapped in the system. The processor takes three T-states to execute this machine cycle. The timing diagram of this cycle is given in Fig. 11.

Fig. 11 Timing diagram I/O write machine cycle

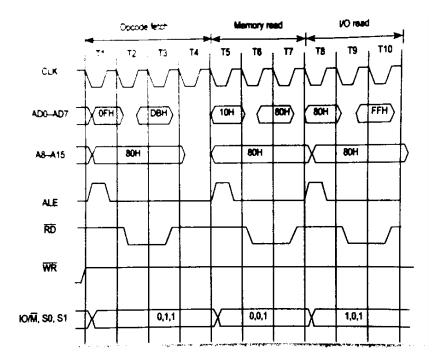

Ex: Timing diagram for IN 80H.

The instruction and the corresponding codes and memory locations are given in Table 5.

| Table 5 IN ins | struction |

|----------------|-----------|

|----------------|-----------|

| Address | Mnemonics | Opcode |

|---------|-----------|--------|

| 800F    | IN 80H    | DB     |

| 8010    |           | 80     |

- i. During the first machine cycle, the opcode DB is fetched from the memory, placed in the instruction register and decoded.

- ii. During second machine cycle, the port address 80H is read from the next memory location.

- iii. During the third machine cycle, the address 80H is placed in the address bus and the data read from that port address is placed in the accumulator.

The timing diagram is shown in Fig. 12.

Fig. 12 Timing diagram for the IN instruction

#### 7. 8085 INTERRUPTS

Interrupt Structure:

Interrupt is the mechanism by which the processor is made to transfer control from its current program execution to another program having higher priority. The interrupt signal may be given to the processor by any external peripheral device.

The program or the routine that is executed upon interrupt is called interrupt service routine (ISR). After execution of ISR, the processor must return to the interrupted program. Key features in the interrupt structure of any microprocessor are as follows:

- i. Number and types of interrupt signals available.

- ii. The address of the memory where the ISR is located for a particular interrupt signal. This address is called interrupt vector address (IVA).

- iii. Masking and unmasking feature of the interrupt signals.

- iv. Priority among the interrupts.

- v. Timing of the interrupt signals.

- vi. Handling and storing of information about the interrupt program (status information).

Types of Interrupts:

Interrupts are classified based on their maskability, IVA and source. They are classified as:

- i. Vectored and Non-Vectored Interrupts

- Vectored interrupts require the IVA to be supplied by the external device that gives the interrupt signal. This technique is vectoring, is implemented in number of ways.

- Non-vectored interrupts have fixed IVA for ISRs of different interrupt signals.

- ii. Maskable and Non-Maskable Interrupts

- Maskable interrupts are interrupts that can be blocked. Masking can be done by software or hardware means.

- Non-maskable interrupts are interrupts that are always recognized; the corresponding ISRs are executed.

- iii. Software and Hardware Interrupts

- Software interrupts are special instructions, after execution transfer the control to predefined ISR.

- Hardware interrupts are signals given to the processor, for recognition as an interrupt and execution of the corresponding ISR.

Interrupt Handling Procedure:

The following sequence of operations takes place when an interrupt signal is recognized:

- i. Save the PC content and information about current state (flags, registers etc) in the stack.

- ii. Load PC with the beginning address of an ISR and start to execute it.

- iii. Finish ISR when the return instruction is executed.

- iv. Return to the point in the interrupted program where execution was interrupted.

Interrupt Sources and Vector Addresses in 8085:

Software Interrupts:

8085 instruction set includes eight software interrupt instructions called Restart (RST) instructions. These are one byte instructions that make the processor execute a subroutine at predefined locations. Instructions and their vector addresses are given in Table 6.

| Instruction | Machine hex code | Interrupt Vector Address |

|-------------|------------------|--------------------------|

| RST 0       | C7               | 0000H                    |

| RST 1       | CF               | 0008H                    |

| RST 2       | D7               | 0010H                    |

| RST 3       | DF               | 0018H                    |

| RST 4       | E7               | 0020H                    |

| RST 5       | EF               | 0028H                    |

| RST 6       | F7               | 0030H                    |

| RST 7       | FF               | 0032H                    |

Table 6 Software interrupts and their vector addresses

The software interrupts can be treated as CALL instructions with default call locations. The concept of priority does not apply to software interrupts as they are inserted into the program as instructions by the programmer and executed by the processor when the respective program lines are read.

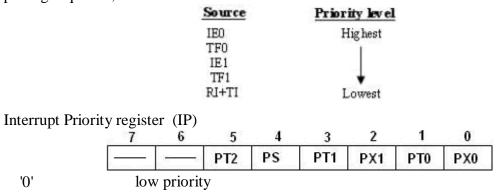

Hardware Interrupts and Priorities:

8085 have five hardware interrupts – INTR, RST 5.5, RST 6.5, RST 7.5 and TRAP. Their IVA and priorities are given in Table 7.

| Interrupt | Interrupt vector    | Maskable or non- | Edge or level | priority |

|-----------|---------------------|------------------|---------------|----------|

|           | address             | maskable         | triggered     |          |

| TRAP      | 0024H               | Non-makable      | Level         | 1        |

| RST 7.5   | 003CH               | Maskable         | Rising edge   | 2        |

| RST 6.5   | 0034H               | Maskable         | Level         | 3        |

| RST 5.5   | 002CH               | Maskable         | Level         | 4        |

| INTR      | Decided by hardware | Maskable         | Level         | 5        |

| Table  | 7 | Hardware | interrunte | of 8085 |

|--------|---|----------|------------|---------|

| I able | 1 | пагижате | menupis    | 01 0005 |

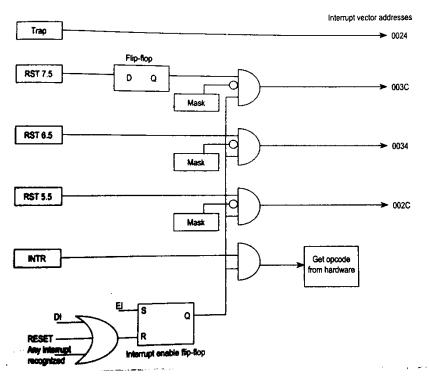

Masking of Interrupts:

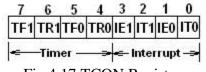

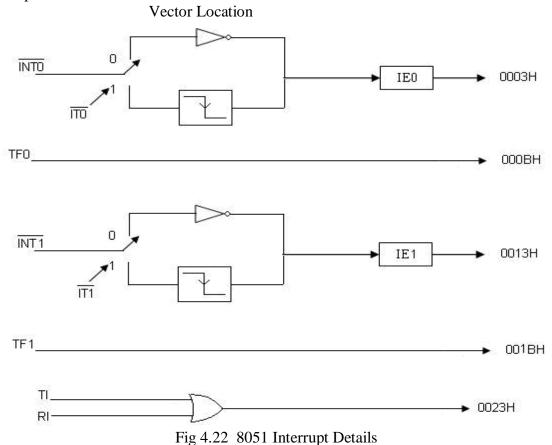

Masking can be done for four hardware interrupts INTR, RST 5.5, RST 6.5, and RST 7.5. The masking of 8085 interrupts is done at different levels. Fig. 13 shows the organization of hardware interrupts in the 8085.

Fig. 13 Interrupt structure of 8085

The Fig. 13 is explained by the following five points:

- i. The maskable interrupts are by default masked by the Reset signal. So no interrupt is recognized by the hardware reset.

- ii. The interrupts can be enabled by the EI instruction.

- iii. The three RST interrupts can be selectively masked by loading the appropriate word in the accumulator and executing SIM instruction. This is called software masking.

- iv. All maskable interrupts are disabled whenever an interrupt is recognized.

- v. All maskable interrupts can be disabled by executing the DI instruction.

RST 7.5 alone has a flip-flop to recognize edge transition. The DI instruction reset interrupt enable flip-flop in the processor and the interrupts are disabled. To enable interrupts, EI instruction has to be executed.

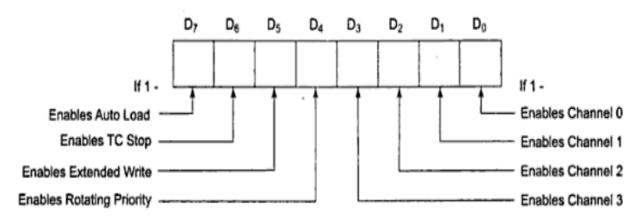

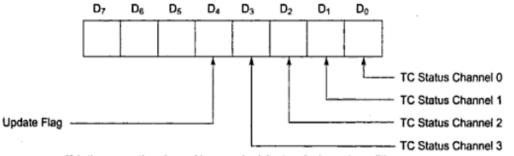

SIM Instruction:

The SIM instruction is used to mask or unmask RST hardware interrupts. When executed, the SIM instruction reads the content of accumulator and accordingly mask or unmask the interrupts. The format of control word to be stored in the accumulator before executing SIM instruction is as shown in Fig. 14.

| Bit position | D7                              | D6                                                      | D5          | D4                            | D3                                                       | D2                  | D1                                   | D0                                   |

|--------------|---------------------------------|---------------------------------------------------------|-------------|-------------------------------|----------------------------------------------------------|---------------------|--------------------------------------|--------------------------------------|

| Name         | SOD                             | SDE                                                     | х           | R7.5                          | MSE                                                      | M7.5                | M6.5                                 | M5.5                                 |

| Explanation  | Serial<br>data<br>to be<br>sent | Serial<br>data<br>enable—<br>set to<br>1 for<br>sending | Not<br>used | Reset<br>RST 7.5<br>flip-flop | Mask set<br>enable—<br>Set to 1<br>to mask<br>interrupts | 1 to<br>mask<br>RST | Set to<br>1 to<br>mask<br>RST<br>6.5 | Set to<br>1 to<br>mask<br>RST<br>5.5 |

Fig. 14 Accumulator bit pattern for SIM instruction

In addition to masking interrupts, SIM instruction can be used to send serial data on the SOD line of the processor. The data to be send is placed in the MSB bit of the accumulator and the serial data output is enabled by making D6 bit to 1.

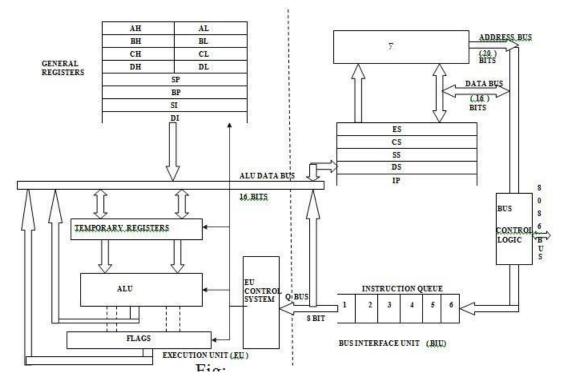

#### **RIM Instruction:**

RIM instruction is used to read the status of the interrupt mask bits. When RIM instruction is executed, the accumulator is loaded with the current status of the interrupt masks and the pending interrupts. The format and the meaning of the data stored in the accumulator after execution of RIM instruction is shown in Fig. 15.

In addition RIM instruction is also used to read the serial data on the SID pin of the processor. The data on the SID pin is stored in the MSB of the accumulator after the execution of the RIM instruction.

| Bit position | D7            | D6     | D5               | D4               | D3                                             | D2               | D1     | D0                                     |

|--------------|---------------|--------|------------------|------------------|------------------------------------------------|------------------|--------|----------------------------------------|

| Name         | SID           | 17.5   | 16.5             | 15.5             | IE                                             | M7.5             | M6.5   | M5.5                                   |

| Explanation  | input<br>data | if RST | if RST<br>6.5 is | if RST<br>5.5 is | Set to<br>1 if<br>interrupts<br>are<br>enabled | if RST<br>7.5 is | 6.5 is | Set to 1<br>if RST<br>5.5 is<br>masked |

Fig. 15 Accumulator bit pattern after execution of RIM instruction

Ex: Write an assembly language program to enables all the interrupts in 8085 after reset.

EI : Enable interrupts

MVI A, 08H : Unmask the interrupts

SIM : Set the mask and unmask using SIM instruction

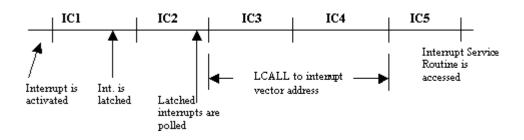

Timing of Interrupts:

The interrupts are sensed by the processor one cycle before the end of execution of each instruction. An interrupts signal must be applied long enough for it to be recognized. The longest instruction of the 8085 takes 18 clock periods. So, the interrupt signal must be applied for at least 17.5 clock periods. This decides the minimum pulse width for the interrupt signal.

The maximum pulse width for the interrupt signal is decided by the condition that the interrupt signal must not be recognized once again. This is under the control of the programmer.

#### **QUESTIONS:**

- 1. What is the function of a microprocessor in a system?

- 2. Why is the data bus in 8085 bidirectional?

- 3. How does microprocessor differentiate between data and instruction?

- How long would the processor take to execute the instruction LDA 1753H if the T-state duration is 2μs?

- 5. Draw the timing diagram of the instruction LDAX B.

- 6. Sketch and explain the various pins of the 8085.

- 7. Explain direct addressing mode of 8085 with an example?

- 8. Draw and explain the timing diagram of the instruction IN 82H.

- 9. What is meant by 'priority of the interrupts'? Explain the operation of the interrupts structure of the 8085, with the help of a circuit diagram.

- 10.Explain the bit pattern for SIM instruction. Write the assembly language program lines to enable all the interrupts in the 8085 after reset.

- 11.Write the logical instructions which affect and which does not affect flags in 8085.

- 12.Write an ALP in 8085 MPU to reject all the negative readings and add all the positive reading from a set of ten reading stored in memory locations starting at XX60H. When the sum exceeds eight bits produce output FFH to PORT1 to indicate overload otherwise display the sum.

- 13.Write an ALP in 8085 to eliminate the blanks (bytes with zero value) from a string of eight data bytes. Use two memory pointers: one to get a byte and the other to store the byte.

- 14.Design an up-down counter to count from 0 to 9 and 9 to 0 continuously with a 1.5 second delay between each count, and display the count at one of the output ports.

#### MODULE: 2

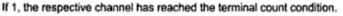

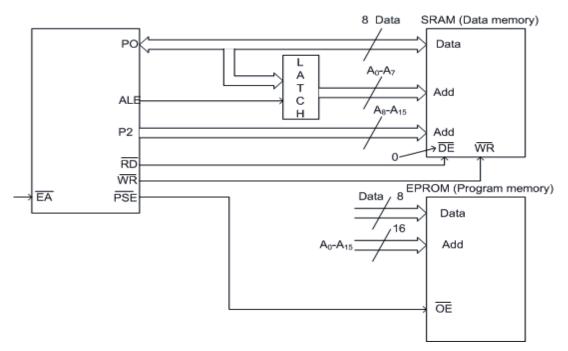

#### 1. INTERFACING MEMORY AND I/O DEVICES WITH 8085

The programs and data that are executed by the microprocessor have to be stored in ROM/EPROM and RAM, which are basically semiconductor memory chips. The programs and data that are stored in ROM/EPROM are not erased even when power supply to the chip is removed. Hence, they are called non-volatile memory. They can be used to store permanent programs.

In a RAM, stored programs and data are erased when the power supply to the chip is removed. Hence, RAM is called volatile memory. RAM can be used to store programs and data that include, programs written during software development for a microprocessor based system, program written when one is learning assembly language programming and data enter while testing these programs.

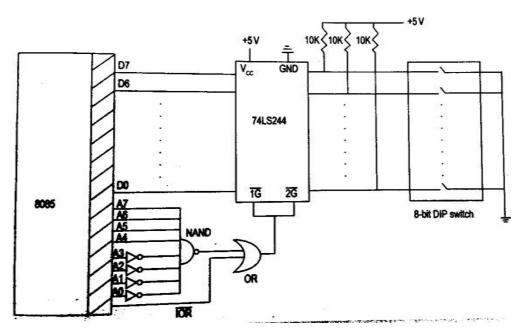

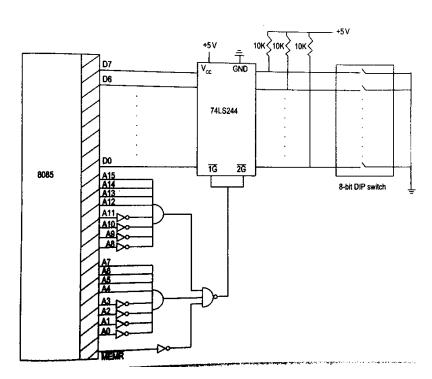

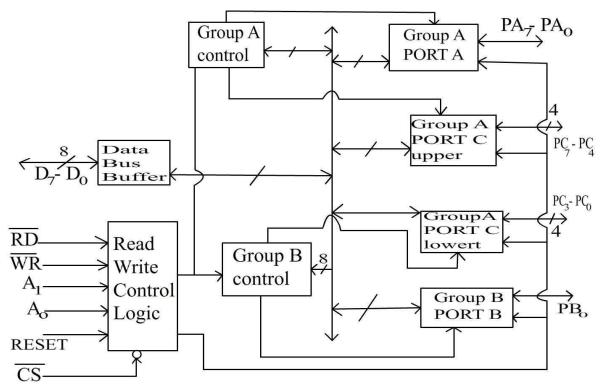

Input and output devices, which are interfaced with 8085, are essential in any microprocessor based system. They can be interfaced using two schemes: I/O mapped I/O and memory-mapped I/O. In the I/O mapped I/O scheme, the I/O devices are treated differently from memory. In the memory-mapped I/O scheme, each I/O device is assumed to be a memory location.

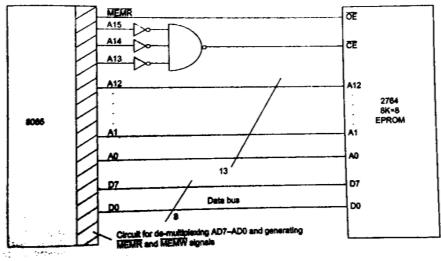

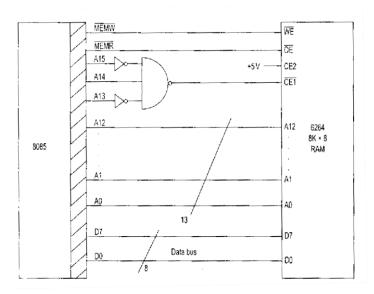

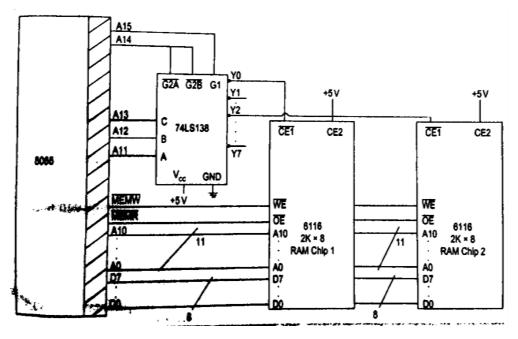

#### 2. INTERFACING MEMORY CHIPS WITH 8085

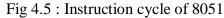

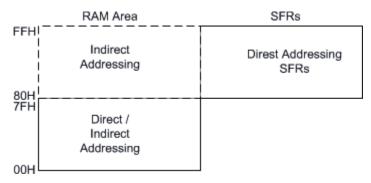

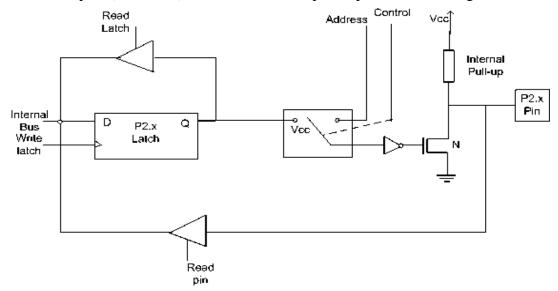

8085 has 16 address lines (A0 - A15), hence a maximum of 64 KB (=  $2^{16}$  bytes) of memory locations can be interfaced with it. The memory address space of the 8085 takes values from 0000H to FFFFH.