# **DIGITALELECTRONICSCIRCUIT**

# **3<sup>rd</sup>SEMESTER-ETC& CSE CVRAMAN POLYTECHNIC**

Prepared by SUCHISMITA SATPATHY DEPT. OF ETC CVRP,BBSR

# **NUMBERSYSTEM AND CODES**

# INTRODUCTION:-

- 1 Thetermdigitalreferstoaprocessthatisachievedbyusingdiscreteunit.

- In numbersystem there are different symbols and each symbol has an absolute value and also has place value.

### RADIXORBASE:-

The radixor baseof anumber systemis defined as the number of different digits which canoccur in each position in the number system.

### RADIXPOINT:-

Thegeneralized form of a decimal point is known as radix point. In any positional number system the radix point divides the integer and fractional part.

Nr=[Integerpart Fractionalpart]

Radixpoint

### NUMBERSYSTEM:-

Ingeneralanumberinasystemhavingbaseorradix 'r'canbewrittenas

an an-1an-2.....a.a.a.1a.2....a.m

Thiswillbeinterpretedas

$Y = a_n x r^n + a_{n-1} x r^{n-1} + a_{n-2} x r^{n-2} + \dots + a_0 x r^0 + a_{-1} x r^{-1} + a_{-2} x r^{-2} + \dots + a_{-m} x r^{-m}$

where Y=valueoftheentirenumber

$a_n$ =the valueofthen<sup>th</sup>digit r =

radix

### TYPESOFNUMBERSYSTEM:-

Therearefourtypesofnumber systems. Theyare

- 1. Decimalnumbersystem

- 2. Binarynumbersystem

- 3. Octalnumbersystem

- 4. Hexadecimalnumbersystem

### **DECIMALNUMBERSYSTEM:-**

- 1 Thedecimalnumbersystemcontain tenunique symbols0,1,2,3,4,5,6,7,8and9. In

- decimal system 10 symbols are involved, so the base or radix is 10.

- Itisapositionalweighted system.

- 1 Thevalueattachedtothesymboldependsonitslocation withrespecttothedecimalpoint.

Ingeneral,

$d_n \quad d_{n-1}d_{n-2}.....d_0.d_{-1}d_{-2}....d_{-m}$

isgiven by

$(d_n x \ 10^n) + (d_{n-1}x \ 10^{n-1}) + (d_{n-2}x \ 10^{n-2}) + \dots + (d_0x \ 10^0) + (d_{-1}x \ 10^{-1}) + (d_{-2}x \ 10^{-2}) + \dots + (d_{-m}x \ 10^{-m})$  For example:-

9256.26=9x1000+2x100+5x10+6x1+2x(1/10)+6x(1/100)

=9x10<sup>3</sup>+2x 10<sup>2</sup>+5 x10<sup>1</sup>+6x10<sup>0</sup>+2x10<sup>-1</sup>+ 6x10<sup>-2</sup>

## **BINARYNUMBERSYSTEM:-**

- 1 Thebinarynumbersystemisapositionalweightedsystem. The

- base or radix of this number system is 2.

- I Ithastwoindependentsymbols.

- The symbols used are 0 and 1.

- A binary digit is called a bit.

- 1 Thebinarypointseparatesthe integerandfractionparts.

Ingeneral,

$d_n \quad d_{n-1}d_{n-2}....d_0.d_{-1}d_{-2}...d_{-k}$

isgiven by

$(d_n x 2^n) + (d_{n-1} x 2^{n-1}) + (d_{n-2} x 2^{n-2}) + \dots + (d_0 x 2^0) + (d_{-1} x 2^{-1}) + (d_{-2} x 2^{-2}) + \dots + (d_{-k} x 2^{-k})$

# **OCTALNUMBERSYSTEM:-**

- I Itisalsoapositionalweightedsystem. Its

- base or radix is 8.

- I Ithas8 independentsymbols0,1,2,3,4,5,6and7.

- I Itsbase8=2<sup>3</sup>,every3-bitgroupofbinary canberepresentedbyanoctaldigit.

# HEXADECIMALNUMBERSYSTEM:-

- 1 Thehexadecimalnumbersystemisapositionalweightedsystem. The

- base or radix of this number system is 16.

- I Thesymbolsusedare0,1,2,3,4,5,6,7,8,9,A,B,C,D,Eand F

- 1 Thebase16 =24 ,every4- bit groupofbinarycanberepresentedbyanhexadecimaldigit.

# CONVERSIONFROMONENUMBERSYSTEMTOANOTHER:-

### 1. <u>BINARYNUMBERSYSTEM</u>:-

### (a) **<u>Binarytodecimalconversion</u>:-**

In this method, each binary digit of the number is multiplied by its positional weight and the product terms are added to obtain decimal number.

#### Forexample:

### (i) Convert(10101)<sub>2</sub>todecimal.

### Solution :

### (ii) Convert(111.101)<sub>2</sub>todecimal.

Solution:

$$\begin{array}{rl} (111.101)_2 & = (1x2^2) + (1x2^1) + (1x2^0) + (1x2^{-1}) + (0x2^{-2}) + (1x2^{-3}) \\ & = 4 + 2 + 1 + 0.5 + 0 + 0.125 \\ & = (7.625)_{10} \end{array}$$

### (b) BinarytoOctalconversion:-

For conversionbinary tooctal thebinarynumbersaredivided intogroupsof 3bitseach, startingatthe binary point and proceeding towards left and right.

| <u>Octal</u> | <b>Binary</b> | <u>Octal</u> | <u>Binary</u> |

|--------------|---------------|--------------|---------------|

| 0            | 000           | 4            | 100           |

| 1            | 001           | 5            | 101           |

| 2            | 010           | 6            | 110           |

| 3            | 011           | 7            | 111           |

Forexample:

### (i) Convert(101111010110.110110011)₂intooctal.

### Solution :

| 011<br>3 |

|----------|

| 3        |

|          |

|          |

|          |

| )        |

|          |

| I        |

### (c) BinarytoHexadecimalconversion:-

For conversionbinary tohexadecimal number thebinarynumbersstartingfrom thebinarypoint, groups are made of 4 bits each, on either side of the binary point.

| <u>Hexadecimal</u> | Binary | <u>Hexadecimal</u> | <b>Binary</b> |

|--------------------|--------|--------------------|---------------|

| 0                  | 0000   | 8                  | 1000          |

| 1                  | 0001   | 9                  | 1001          |

| 2                  | 0010   | А                  | 1010          |

| 3                  | 0011   | В                  | 1011          |

| 4                  | 0100   | С                  | 1100          |

| 5                  | 0101   | D                  | 1101          |

| 6                  | 0110   | E                  | 1110          |

| 7                  | 0111   | F                  | 1111          |

### Forexample:

(i) Convert(1011011011)<sub>2</sub>intohexadecimal.

### Solution:

| GivenBinary number             | 10   | 1101 | 1011 |

|--------------------------------|------|------|------|

| Groupof4bitsare                | 0010 | 1101 | 1011 |

| Converteachgroupinto hex       | = 2  | D    | В    |

| Theresultis(2DB) <sub>16</sub> |      |      |      |

### (ii) Convert(01011111011.011111)2intohexadecimal.

### Solution:

| GivenBinary number         | 010   | 1111 | 1011 | • | 0111 | 11   |

|----------------------------|-------|------|------|---|------|------|

| Groupof3bitsare            | =0010 | 1111 | 1011 |   | 0111 | 1100 |

| Converteachgroupintooctal= | 2     | F    | В    | • | 7    | С    |

Theresultis(2FB.7C)<sub>16</sub>

### 2. DECIMALNUMBER SYSTEM:-

### (a) Decimaltobinaryconversion:-

In the conversion the integer number are converted to the desired base using successive division by the base or radix.

### Forexample:

### (i) Convert(52)<sub>10</sub>intobinary.

### Solution:

Divide the given decimal number successively by 2 read the integer part remainder upwards to get equivalentbinary number. Multiply the fraction part by 2. Keep the integer in the product asit is and multiply the new fraction in the product by 2. The process is continued and the integer are read in the products from top to bottom.

$\begin{array}{cccc} 2\underline{152} \\ 2\underline{126} & -0 \\ 2\underline{113} & -0 \\ 2\underline{16} & -1 \\ 2\underline{13} & -0 \\ 2\underline{11} & -1 \\ 0 & -1 \end{array}$

### Resultof(52)<sub>10</sub>is (110100)<sub>2</sub> (ii) Convert(105.15)<sub>10</sub>intobinary.

### Solution:

| Integer       | rpart          | Fraction part |

|---------------|----------------|---------------|

| 2 <u> 105</u> |                | 0.15x2=0.30   |

| 2 <u>152</u>  | <sup>—</sup> 1 | 0.30x2=0.60   |

| 2 <u>l26</u>  | _0             | 0.60x2=1.20   |

| 2 <u> 13</u>  | _0             | 0.20x2=0.40   |

| 2 <u>l6</u>   | <sup>—</sup> 1 | 0.40x2=0.80   |

| 2 <u> 3</u>   | _0             | 0.80x2=1.60   |

| 2 <u> 1</u>   | <sup>—</sup> 1 |               |

| 0             | <sup>—</sup> 1 |               |

|               |                |               |

Resultof(105.15)<sub>10</sub>is(1101001.001001)<sub>2</sub>

### (b) Decimaltooctalconversion:-

To convert the given decimal integer number to octal, successively divide the given number by 8 till the quotient is 0. To convert the given decimal fractions to octal successively multiply the decimal fraction and the subsequent decimal fractions by 8 till the product is 0 or till the required accuracy is obtained.

### Forexample:

(i) Convert(378.93)<sub>10</sub>intooctal.

### Solution:

| 8 <u>1378</u> |          | 0.93x8=7.44 |

|---------------|----------|-------------|

| 8 <u>l47</u>  | <u> </u> | 0.44x8=3.52 |

| 8 <u>15</u>   | — 7      | 0.52x8=4.16 |

| 0             | <u> </u> | 0.16x8=1.28 |

Resultof(378.93)10is(572.7341)8

### (c) Decimaltohexadecimalconversion:-

Thedecimaltohexadecimalconversionissameasoctal.

### Forexample:

(i) Convert(2598.675)<sub>10</sub>intohexadecimal.

Solution:

|                    | Remaiı<br>Decima |        |                                | Hex    |

|--------------------|------------------|--------|--------------------------------|--------|

| 16 <u> 2598</u>    |                  |        | 0.675x16=10.8                  | А      |

| 16 <u> 162</u>     | —6               | 6      | 0.800x16=12.8                  | С      |

| 16 <u> 10</u><br>0 | —2<br>— 10       | 2<br>A | 0.800x16=12.8<br>0.800x16=12.8 | C<br>C |

Resultof(2598.675)10is(A26.ACCC)16

### 3. OCTAL NUMBER SYSTEM:-

### (a) Octaltobinaryconversion:-

To convertagive naoctal number to binary, replace each octal digit by its3-bit binary equivalent.

#### Forexample:

#### Convert(367.52)<sub>8</sub>intobinary.

| Solution:<br>GivenOctalnumberis | 3    | 6  | 7    |     | 5    | 2 |

|---------------------------------|------|----|------|-----|------|---|

| Converteachgroupoctal to binary | =011 | 11 | 0111 | .10 | 1010 | ) |

Resultof(367.52)8is(011110111.101010)2

### (b) Octaltodecimal conversion:-

Forconversionoctaltodecimalnumber, multiplyeachdigitin theoctalnumberby theweightof its position and add all the product terms

Forexample: -

# Convert(4057.06)<sub>8</sub>todecimal

Solution:

$\begin{array}{rcrcrc} (4057.06)_8 & = & 4x8^3 + 0x8^2 + 5x8^1 + 7x8^0 + 0x8^{-1} + 6x8^{-2} \\ & = & 2048 + 0 + 40 + 7 + 0 + 0.0937 \end{array}$

= (2095.0937)<sub>10</sub>

#### Resultis(2095.0937)10

### (c) Octaltohexadecimalconversion:-

Forconversion of octal to Hexadecimal, first convert the given octal number to binary and then binary number to hexadecimal.

Forexample:-

#### Convert(756.603)<sub>8</sub>tohexadecimal.

| Solution:-                     |   |      |      |      |   |      |      |      |

|--------------------------------|---|------|------|------|---|------|------|------|

| Givenoctal no.                 |   | 7    | 5    | 6    | - | 6    | 0    | 3    |

| Convert eachoctaldigittobinary | = | 111  | 101  | 110  |   | 110  | 000  | 011  |

| Group of 4bits are             | = | 0001 | 1110 | 1110 |   | 1100 | 0001 | 1000 |

| Convert4bitsgrouptohex.        | = | 1    | Е    | Е    |   | С    | 1    | 8    |

Resultis(1EE.C18)16

### (4)<u>HEXADECIMALNUMBERSYSTEM</u>:-(a)<u>Hexadecimaltobinaryconversion</u>:-

For conversion of hexadecimal to binary, replace hexadecimal digit by its 4 bit binary group.

Forexample:

#### Convert(3A9E.B0D)<sub>16</sub>intobinary.

| Solution:<br>GivenHexadecimalnumberis   | 3      | A      | 9     | Е     | •    | В     | 0          | D |

|-----------------------------------------|--------|--------|-------|-------|------|-------|------------|---|

| Convert each hexadecimal<br>4 bitbinary | = 0011 | 101010 | 01111 | 0.101 | 1000 | 00110 | 1 digit to |   |

Resultof(3A9E.B0D)8is(0011101010011110.101100001101)2

### (b) Hexadecimaltodecimalconversion:-

Forconversion of hexadecimal to decimal, multiply each digit in the hexadecimal number by its position weight and add all those product terms.

#### Forexample: -Convert(A0F9.0EB)<sub>16</sub>todecimal

### Solution:

$\begin{array}{rcl} (\mathsf{A0F9.0EB})_{16} &= (10 \times 16^3) + (0 \times 16^2) + (15 \times 16^1) + (9 \times 16^0) + (0 \times 16^{-1}) + (14 \times 16^{-2}) + (11 \times 16^{-3}) \\ &= & 40960 + 0 + 240 + 9 + 0 + 0.0546 + 0.0026 \\ &= & (41209.0572)_{10} \end{array}$

### Resultis(41209.0572)<sub>10</sub> (c) <u>HexadecimaltoOctalconversion</u>:-

For conversion of hexadecimal tooctal, first convert the given hexadecimal number to binary and then binary number to octal.

#### Forexample:-Convert(B9F.AE)<sub>16</sub>tooctal.

| Solution:-                   |   |       |      |                   |     |      |       |    |

|------------------------------|---|-------|------|-------------------|-----|------|-------|----|

| Givenhexadecimalno.is        |   | В     | 9    | F                 | =   | А    | E     |    |

| Converteachhex.digittobinary | = | 1011  | 1001 | 11                | 111 | 1010 | 111   | 10 |

| Groupof3bitsare              | = | 10111 | 0 0  | )111 <sup>.</sup> | 11  | 1010 | 11100 | )  |

| Convert3bitsgrouptooctal.    | = | 5     | 6    | 3                 | 7   | 5    | 3     | 4  |

Result is (5637.534)8

### BINARYARITHEMATICOPERATION:-

### 1. BINARY ADDITION:-

Thebinaryaddition rulesareasfollows 0+0=0;0+1=1;1+0=1;1+1=10,i.e0witha carryof1

### Forexample:-

Add(100101)<sub>2</sub>and(1101111)<sub>2</sub>. Solution:-

Resultis(10010100)2

### 2. BINARYSUBTRACTION:-

Thebinarysubtractionrulesareasfollows 0-0=0; 1-1=0;1-0=1; 0-1=1, witha borrowof1

Forexample:-Substract(111.111)<sub>2</sub>from(1010.01)<sub>2</sub>. Solution :-

> 10 1 0.0 1 0 - <u>1 1 1. 1 1 1</u> <u>00 10.0 11</u>

Resultis(0010.011)2

### 3. BINARYMULTIPLICATION:-

The binary multiplication rules are as follows  $0 \times 0 = 0$ ;  $1 \times 1 = 1$ ;  $1 \times 0 = 0$ ;  $0 \times 1 = 0$ For example:-

#### Multiply(1101)<sub>2</sub>by(110)<sub>2</sub>. Solution :-

$$\begin{array}{r}

11 \ 0 \ 1 \\

\times \ 110 \\

00 \ 0 \ 0 \\

11 \ 0 \ 1 \\

+ \ 110 \ 1 \\

10 \ 01 \ 11 \ 0 \\

\end{array}$$

Resultis(1001110)2

### 4. BINARY DIVISION:-

Thebinarydivisionisverysimpleandsimilartodecimalnumbersystem. The division by '0' is meaningless. Sowehave only 2 rules

0÷1 =0 1÷1 =1 Forexample:-Divide(10110)<sub>2</sub>by(110)<sub>2</sub>. Solution

:-

Resultis(111.1)2

# 1'sCOMPLEMENTREPRESENTATION:-

The1's complement of a binary number is obtained by changing each 0 to 1 and each 1 to 0.

### Forexample:-

Find(1100)<sub>2</sub>1'scomplement.

### Solution:-

| Given           | 1 | 1 | 0 | 0 |

|-----------------|---|---|---|---|

| 1'scomplementis | 0 | 0 | 1 | 1 |

Resultis(0011)2

# 2'sCOMPLEMENTREPRESENTATION:-

The2'scomplement of a binary number is a binary number which is obtained by adding1 to the 1's complement of a number i.e.

2'scomplement=1'scomplement +1

### Forexample:-

Find(1010)<sub>2</sub>2'scomplement.

### Solution:-

| Given           |   | 1 | 0 | 1 | 0 |

|-----------------|---|---|---|---|---|

| 1'scomplementis |   | 0 | 1 | 0 | 1 |

| rocomplementio  | + | U |   | U | 1 |

| 2'scomplement   |   | 0 | 1 | 1 | 0 |

|                 |   |   |   |   |   |

Resultis(0110)2

### <u>SIGNEDNUMBER</u>:-

In sign –magnitude form,additionalbit calledthesignbit isplaced infrontof thenumber. If the signbit is 0, the number is positive. If it is a 1, the number is negative.

### Forexample:-

0 1 0 1 0 0 1= +41 ↑ Signbit 1 1 0 1 0 0 1= -41 ↑ Signbit

### SUBSTRACTIONUSINGCOMPLEMENTMETHOD:-

### **<u>1's COMPLEMENT</u>:-**

In 1's complement subtraction, add the 1's complement of subtrahend to the minuend. If there is a carry out, then the carry is added to the LSB. This is called end around carry. If the MSB is 0, the result is positive. If the MSB is 1, the result is negative and is in its 1's complement form. Then take its 1's complement to get the magnitude in binary.

Forexample:-

Subtract(10000)<sub>2</sub>from(11010)<sub>2</sub>using1'scomplement.

$\begin{array}{rcrcr} 11010 & 11010 & = 26 \\ -10000 & => & + \underline{01111} & (1's \ complement) & = - \underline{16} \\ Carry & \rightarrow & 101001 & + 10 \\ & + \underline{& 1} \\ & \underline{01010} & = + 10 \end{array}$

Resultis+10

Solution:-

### 2's COMPLEMENT:-

In 2's complement subtraction, add the 2's complement of subtrahend to the minuend. If there is a carry out, ignoreit. If the MSB 0, theresult is positive. If the MSB 1, theresult is negative and is inits 2's complement form. Then take its 2's complement to get the magnitude in binary.

### Forexample:-

### Subtract(1010100)<sub>2</sub>from(1010100)<sub>2</sub>using2'scomplement.

Solution:-

|    | 10 1 0 10 0                                           |    | 10 1 0 10 0                         |  | = | 84          |  |  |  |

|----|-------------------------------------------------------|----|-------------------------------------|--|---|-------------|--|--|--|

| -  | 10 1 0 10 0                                           | => | + <u>0 101 10 0(</u> 2'scomplement) |  | = | - <u>84</u> |  |  |  |

|    |                                                       |    | = 0(result=0)                       |  |   | <u>0</u>    |  |  |  |

| He | Hence MSB is0. Theanswerispositive.So itis+0000000 =0 |    |                                     |  |   |             |  |  |  |

### DIGITALCODES:-

In practice the digital electronics requires to handle data which may be numeric, alphabets and special characters. This requires the conversion of the incoming data into binary format before it can be processed. There is various possible ways of doing this and this process is called encoding. To achieve the reverse of it,we use decoders.

### WEIGHTEDANDNON-WEIGHTEDCODES:-

Therearetwotypesofbinary codes

- 1) Weightedbinary codes

- 2) Non-weightedbinary codes

Inweighted codes, foreach position (orbit), there is specific weight attached.

Forexample, inbinary number, each bitis assigned particular weight 2n where 'n' is the bit number forn =

0,1,2,3,4theweightsare1,2,4,8,16 respectively.

Example :- BCD

Non-weightedcodesarecodeswhicharenotassigned withany weighttoeachdigitposition, i.e.,each digit position within the number is not assigned fixed value. Example:-Excess-3(XS-3)codeandGraycodes

Example:-Excess-3(XS-3)codeandGraycodes

### BINARYCODEDDECIMAL(BCD):-

BCD is a weighted code. In weighted codes, each successive digitfrom right to left represents weights equal to some specified value and to get the equivalent decimal number add the products of the weights by the corresponding binary digit. 8421 is the most common because 8421 BCD is the most natural amongst theother possible codes.

#### Forexample:-

(567)<sub>10</sub>isencodedinvarious4bitcodes.

Solution:-

| Decimal  | $\rightarrow$ | 5    | 6    | 7    |

|----------|---------------|------|------|------|

| 8421code | $\rightarrow$ | 0101 | 0110 | 0111 |

| 6311code | $\rightarrow$ | 0111 | 1000 | 1001 |

| 5421code | $\rightarrow$ | 1000 | 0100 | 1010 |

### **BCDADDITION:-**

Additionof BCD (8421) is performedbyaddingtwo digits of binary, startingfrom least significant digit. In case if the result is an illegal code (greater than 9) or if there is a carry out of one then add 0110(6) and add the resulting carry to the next most significant.

### Forexample:-

### Add679.6from536.8usingBCDaddition.

### Solution:-

| 67 9.6           |       | 01100          | 11110 | 01.011 | 0    |          | ( 679.6inBCD)          |  |  |  |

|------------------|-------|----------------|-------|--------|------|----------|------------------------|--|--|--|

| + <u>5 3 6.8</u> | =>+   | 010100         | 11    | 0110   | .100 | 0        | (536.8 in BCD)         |  |  |  |

| 12 1 6.4         |       | 10111          | 010   | 1111   | .111 | 0        | (Allareillegalcodes)   |  |  |  |

|                  | -     | <u>+ 0110+</u> | 0110+ | 0110.+ | -011 | <u>0</u> | (Add0110toeach)        |  |  |  |

|                  | 0001  | 0010           | 0001  | 0110.0 | )100 |          |                        |  |  |  |

|                  | 1     | 2              | 1     | 6      |      | 4        | (correctedsum =1216.4) |  |  |  |

| Resultis12       | 216.4 |                |       |        |      |          |                        |  |  |  |

### **BCDSUBTRACTION:-**

The BCD subtraction is performed by subtracting the digits of each 4 –bit group of the subtrahend from corresponding 4 –bit group of the minuend in the binary starting from the LSD. If there is no borrow from the next higher group[ then no correction is required. If there is a borrow from the next group, then  $6_{10}(0110)$  is subtracted from the difference term of this group.

# Forexample:-

### Subtract147.8from206.7using8421BCDcode.

| Solution:-     |                     |        |       |    |                                       |  |  |  |

|----------------|---------------------|--------|-------|----|---------------------------------------|--|--|--|

| 206.7          | 00100000            | 0110   | .0111 |    | ( 206.7in BCD)                        |  |  |  |

| - <u>147.8</u> | =>- <u>00010100</u> | 011    | 1.100 | 0  | _(147.8inBCD)                         |  |  |  |

| 58.9           | 0000101111          | 10.111 | 1     |    | (Borrowsarepresent)                   |  |  |  |

|                | -01                 | 10-011 | 001   | 10 |                                       |  |  |  |

|                |                     | 010110 | 00.10 | 01 |                                       |  |  |  |

|                | 5                   | 8      |       | 9  | (correcteddifference=58.9)            |  |  |  |

|                |                     |        |       |    | · · · · · · · · · · · · · · · · · · · |  |  |  |

Resultis(58.9)10

### EXCESSTHREE(XS-3)CODE:-

The Excess-3 code, also called XS-3, is a non- weighted BCD code. This derives it name from the fact thateach binary code word is the corresponding 8421 code word plus 0011(3). It is a sequential code. It is a self complementing code.

### XS-3ADDITION:-

In XS-3 addition, add the XS-3 numbers by adding the 4 bit groups in each column starting from the LSD. If there is no carry out from the addition of any of the 4 bit groups, subtract 0011 from the sum term of those groups. If there is a carry out, add 0011 to the sum term of those groups

#### Forexample:-

#### Add37and28usingXS-3code.

| 37           |    | 01101010                         | (37inXS-3)                                            |

|--------------|----|----------------------------------|-------------------------------------------------------|

| + <u>2 8</u> | => | + <u>01011011</u>                | (28inXS-3)                                            |

| 65           |    | 1011 <b>1</b> 1010               | (Carry is generated)<br>(Propagatecarry)              |

|              |    | 1100 0101                        | (Add0110tocorrect0101and                              |

|              |    | - <u>0011 +0011</u><br>1001 1000 | subtract0011tocorrect1100) (Correctedsum inXS-3=6510) |

|              |    |                                  | ( · · · · · · · · · · · · · · · · · · ·               |

### XS-3SUBTRACTION:-

To subtract in XS-3 number by subtracting each 4-bit group of the subtrahend from the corresponding 4-bit group of the minuend starting from the LSD. If there is no borrow from the next 4-bit group. add 0011 to the difference term of such groups. If there is a borrow, subtract 0011 from the difference term.

#### Forexample:-

#### Subtract175from267usingXS-3code.

| <b>Solution :-`</b><br>267 |    | 010110                   | 10   | 1010 | (267inXS-3)                                                      |

|----------------------------|----|--------------------------|------|------|------------------------------------------------------------------|

| 207                        |    | 010110                   | 10   | 1010 | (20/11/3-3)                                                      |

| <u>-175</u>                | => | - <u>01001</u>           | 010  | 100  | <u>0(</u> 175inXS-3)                                             |

| 092                        |    | 000011<br><u>+0011-0</u> |      |      | (Correct0010and0000byadding0011and correct1111bysubtracting0011) |

|                            |    | 0011                     | 1100 | 0101 | (Correcteddifference inXS-3=92 <sub>10</sub> )                   |

### ASCIICODE:-

The American Standard Code for Information Interchange (ASCII) pronounced as 'ASKEE' is widely used alphanumeric code. This is basically a 7 bit code. The number of different bit patterns that can be created with 7 bits is 27 = 128, the ASCII can be used to encode both the uppercase and lowercase characters of the alphabet(52symbols) and some special symbols inaddition to the 10 decimal digits. It is shown below shows the ASCII groups.

| LSBs | MSBs |     |       |     |     |     |     |     |  |  |  |  |

|------|------|-----|-------|-----|-----|-----|-----|-----|--|--|--|--|

|      | 000  | 001 | 010   | 011 | 100 | 101 | 110 | 111 |  |  |  |  |

| 0000 | NUL  | DEL | Space | 0   | @   | Р   | Р   |     |  |  |  |  |

| 0001 | SOH  | DC1 | !     | 1   | А   | Q   | а   | q   |  |  |  |  |

| 0010 | STX  | DC2 | "     | 2   | В   | R   | b   | r   |  |  |  |  |

| 0011 | ETX  | DC3 | #     | 3   | С   | S   | С   | S   |  |  |  |  |

| 0100 | EOT  | DC4 | \$    | 4   | D   | Т   | d   | t   |  |  |  |  |

#### TheASCIIcode

| 0101 | ENQ | NAK | % | 5 | E | U | е | u   |

|------|-----|-----|---|---|---|---|---|-----|

| 0110 | ACK | SYN | & | 6 | F | V | f | v   |

| 0111 | BEL | ETB | " | 7 | G | W | g | w   |

| 1000 | BS  | CAN | ( | 8 | Н | Х | h | х   |

| 1001 | HT  | EM  | ) | 9 | I | Y | i | у   |

| 1010 | LF  | SUB | * | : | J | Z | j | z   |

| 1011 | VT  | ESC | + | ; | К | [ | k | {   |

| 1100 | FF  | FS  | , | < | L | ١ | Ι |     |

| 1101 | CR  | GS  | - | = | М | ] | m | }   |

| 1110 | SO  | RS  | • | > | N | ^ | n | ~   |

| 1111 | SI  | US  | 1 | ? | 0 | _ | 0 | DLE |

### **EBCDICCODE:**-

The Extended Binary Coded Decimal Interchange Code (EBCDIC) pronounced as 'eb –si- dik' is an 8 bit alphanumeric code.Since28= 256bitpatterns canbe formedwith8 bits.Itis used by mostlargecomputers to communicate in alphanumeric data. The table shown below shows the EBCDIC code.

| LSD<br>(Hex) | MSD(I | MSD(Hex) |     |     |    |    |   |   |   |   |   |   |   |   |   |   |

|--------------|-------|----------|-----|-----|----|----|---|---|---|---|---|---|---|---|---|---|

|              | 0     | 1        | 2   | 3   | 4  | 5  | 6 | 7 | 8 | 9 | А | В | С | D | E | F |

| 0            | NUL   | DLE      | DS  |     | SP | &  |   |   |   |   |   |   | [ | ] | ١ | 0 |

| 1            | SOH   | DC1      | SOS |     |    |    | / |   | а | j | ~ |   | А | J |   | 1 |

| 2            | STX   | DC2      | FS  | SYN |    |    |   |   | b | k | S |   | В | K | S | 2 |

| 3            | ETX   | DC3      |     |     |    |    |   |   | с | I | t |   | С | L | Т | 3 |

| 4            | PF    | RES      | BYP | PN  |    |    |   |   | d | m | u |   | D | М | U | 4 |

| 5            | HT    | NL       | LF  | RS  |    |    |   |   | е | n | v |   | E | Ν | V | 5 |

| 6            | LC    | BS       | EOB | YC  |    |    |   |   | f | 0 | w |   | F | 0 | W | 6 |

| 7            | DEL   | IL       | PRE | EOT |    |    |   |   | g | р | х |   | G | Р | Х | 7 |

| 8            |       | CAN      |     |     |    |    |   |   | h | q | у |   | Н | Q | Y | 8 |

| 9            |       | EM       |     |     |    |    |   |   | i | r | z |   | Ι | R | Z | 9 |

| А            | SMM   | CC       | SM  |     | Ø  | !  | Ι | : |   |   |   |   |   |   |   |   |

| В            | VT    |          |     |     | •  | \$ | , | # |   |   |   |   |   |   |   |   |

| С            | FF    | IFS      |     | DC4 | <  | *  | % | @ |   |   |   |   |   |   |   |   |

| D            | CR    | IGS      | ENQ | NAK | (  | )  | _ | " |   |   |   |   |   |   |   |   |

| E            | SO    | IRS      | ACK |     | +  | ;  | > | = |   |   |   |   |   |   |   |   |

| F            | SI    | IUS      | BEL | SUB | Ι  | 6  | ? | " |   |   |   |   |   |   |   |   |

#### TheEBCDICcode

# **GRAYCODE:**-

Thegraycode isanon-weighted code. It is notaBCDcode. It is cyclic code because successive words in this differ in one bit position only i.e it is a unit distance code.

Gray code is used in instrumentation and data acquisition systems where linear orangulardisplacement is measured. They are also used in shaft encoders, I/O devices, A/D converters and other peripheral equipment.

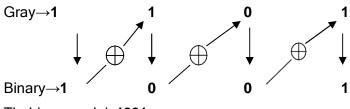

### BINARY-TO-GRAY CONVERSION:-

$If ann-bit binary number is represented by B_n B_{n-1--} - - B_1 and its gray code equivalent by G_n G_{n-1} - - - G_1, where B_n and G_n are the MSBs , then gray code bits are obtained from the binary code as follows G_n = B_n$

G<sub>n-1</sub>=B<sub>n</sub>⊕B<sub>n-1</sub> .

•

$G_1 = B_2 \oplus B_1$

Wherethesymbol<sup>®</sup>standsforExclusiveOR(X-OR)

#### Forexample:-

Convertthe binary1001totheGraycode.

Solution:-`

| Binary→ <b>1</b> |   | -⊕•0 | -⊕•0 | $- \oplus $ | 1 |

|------------------|---|------|------|-------------|---|

|                  | ↓ | Ļ    |      | Ļ           | ↓ |

| Gray→            | 1 | 1    |      | 0           | 1 |

Thegraycodeis1101

### **GRAY-TO-BINARY CONVERSION:-**

If ann-bitgray number is represented by  $G_nG_{n-1}$ ------  $G_1$  and its binary equivalent by  $B_nB_{n-1}$ -------  $B_1$ , then binary bits are obtained from Gray bits as follows :  $B_n$

$= G_{n}$   $B_{n-1} = B_{n} \oplus G_{n-1}$   $\vdots$   $B_{1} = B_{2} \oplus G_{1}$

Forexample:-

# ConverttheGraycode1101tothebinary.

Solution:-

Thebinary codeis1001

# **LOGICGATES**

# LOGICGATES:-

- 1 Logicgatesarethefundamentalbuildingblocks of digital systems. There

- are 3 basic types of gates AND, OR and NOT.

- Logic gates are electronic circuits because they are made up of a number of electronic devices and components.

- Inputs and outputs of logic gates can occuronly in 2 levels. These two levels are termed HIGH and LOW, or TRUE and FALSE, or ON and OFF or simply 1 and 0.

- <sup>1</sup> Thetable which listsall thepossible combinations of input variables and the corresponding outputs is called a truth table.

### LEVEL LOGIC:-

Alogicin which the voltage levels represents logic1 and logic0. Level logic may be positive or negative logic. **PositiveLogic:**

A positivelogicsystem is theone in which the higher of the two voltage levels represents the logic1 and the lower of the two voltages level represents the logic 0.

### NegativeLogic:-

A negativelogicsystemistheone in which thelowerof the two voltage levelsrepresents the logic1 and the higher of the two voltages level represents the logic 0.

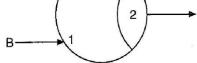

# DIFFERENTTYPESOFLOGICGATES:-

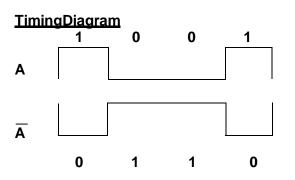

### NOT GATE (INVERTER):-

- A NOTgate, also calledand inverter, hasonlyone inputandoneoutput. It is

- a device whose output is always the complement of its input.

- Theoutputof a NOTgate is the logic1 state when its input is in logic0 state and the logic0 state when its inputs is in logic 1 state.

ICNo.:-7404

LogicSymbol

out

| INPUT<br>A | OU <u>TP</u> UT<br>A |

|------------|----------------------|

| 0          | 1                    |

| 1          | 0                    |

**Truthtable**

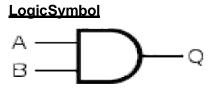

# ANDGATE:-

- I AnAND gatehastwoor moreinputsbutonlyoneoutput.

- 1 Theoutput islogic1 stateonlywhen each one of its inputsisat logic1 state. The

- I output is logic 0 state even if one of its inputs is at logic 0 state.

# ICNo.:-7408

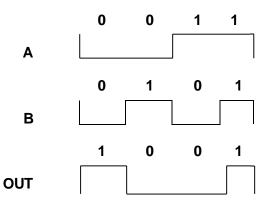

### **TimingDiagram**

| <u>TruthTable</u> |   |       |  |  |

|-------------------|---|-------|--|--|

| OUTPUT            |   |       |  |  |

| Α                 | В | Q=A.B |  |  |

| 0                 | 0 | 0     |  |  |

| 0                 | 1 | 0     |  |  |

| 1                 | 0 | 0     |  |  |

| 1                 | 1 | 1     |  |  |

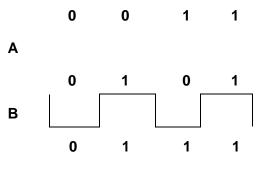

# ORGATE:-

- I AnOR gatemayhavetwoor moreinputsbutonlyoneoutput.

- I Theoutput islogic1 state, even if one of its input is in logic1 state.

- 1 Theoutputislogic0state,onlywheneachoneofitsinputsisinlogicstate.

#### ICNo.:-7432 LogicSymbol

### TruthTable

| I | INF | PUT | OUTPUT |

|---|-----|-----|--------|

|   | Α   | В   | Q=A+B  |

| ſ | 0   | 0 0 |        |

| Ī | 0   | 1   | 1      |

| ſ | 1   | 0   | 1      |

|   | 1   | 1   | 1      |

### **TimingDiagram**

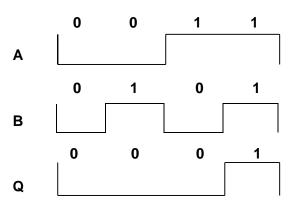

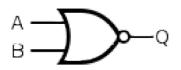

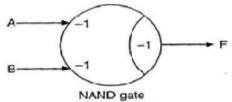

# NANDGATE:-

- I NANDgateisacombinationofanANDgateandaNOTgate.

- Theoutput is logic0 when eachof the input is logic 1andfor anyothercombination of inputs, the output is logic 1.

- IC No.:- 7400 two input NAND gate 7410threeinputNANDgate 7420 four input NAND gate 7430eightinputNANDgate

### LogicSymbol

### TruthTable

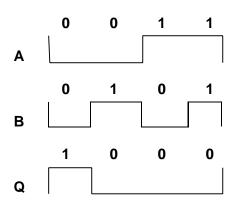

| INPUT |   | OUTPUT |  |

|-------|---|--------|--|

| Α     | В | Q= A.B |  |

| 0     | 0 | 1      |  |

| 0     | 1 | 1      |  |

| 1     | 0 | 1      |  |

| 1     | 1 | 0      |  |

### TimingDiagram

#### Q

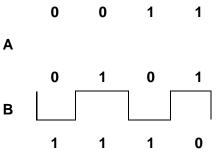

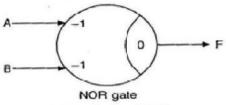

### NORGATE:-

- NORgateis acombinationofanORgateandaNOTgate.

- Theoutput is logic1,onlywheneachoneof itsinputis logic 0andforanyother combination f inputs, the output is a logic 0 level.

### IC No.:- 7402 two input NOR gate 7427threeinputNORgate 7425 four input NOR gate

### LogicSymbol

### TruthTable

| INPUT |   | OUTPUT |

|-------|---|--------|

| Α     | В | Q=A+B  |

| 0     | 0 | 1      |

| 0     | 1 | 0      |

| 1     | 0 | 0      |

| 1     | 1 | 0      |

### **TimingDiagram**

# EXCLUSIVE-OR(X-OR)GATE:-

- AnX-ORgateisatwoinput, one output logic circuit.

- Theoutput is logic1 when oneandonlyoneof its two inputs is logic1. When both the inputs is logic 0 or when both the inputs is logic 1, the output is logic 0.

ICNo.:-7486

LogicSymbol

INPUTSareAandB

OUTPUTis**Q**=A⊕B

=A B+A B

### TimingDiagram

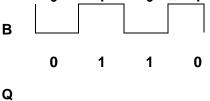

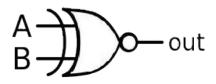

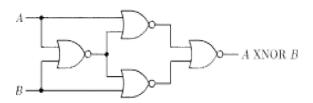

### EXCLUSIVE-NOR(X-NOR)GATE:-

- I AnX-NORgate isthecombination of anX-ORgate and a NOTgate. An

- I X-NOR gate is a two input, one output logic circuit.

- I Theoutput is logic1only whenboth theinputsarelogic0or whenboth the inputs is1. The

- I output is logic 0 when one of the inputs is logic 0 and other is1.

### TruthTable

| INF | νUT | OUTPUT |  |

|-----|-----|--------|--|

| Α   | В   | Q=A⊕B  |  |

| 0   | 0   | 0      |  |

| 0   | 1   | 1      |  |

| 1   | 0   | 1      |  |

| 1   | 1   | 0      |  |

LogicSymbol

OUT=AB+AB

=AXNORB

**TimingDiagram**

| INPUT |   | OUTPUT      |  |

|-------|---|-------------|--|

| A B   |   | OUT=A XNORB |  |

| 0     | 0 | 1           |  |

| 0     | 1 | 0           |  |

| 1     | 0 | 0           |  |

| 1     | 1 | 1           |  |

### **UNIVERSALGATES:-**

There are 3 basic gates AND, OR and NOT, there are two universal gates NAND and NOR, each of which can realize logic circuits single handedly. The NAND and NOR gates are called universal building blocks. Both NAND and NOR gates can perform all logic functions i.e. AND, OR, NOT, EXOR and EXNOR.

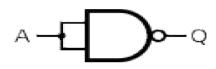

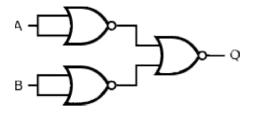

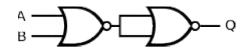

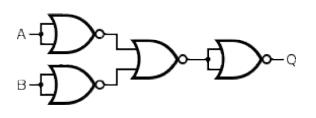

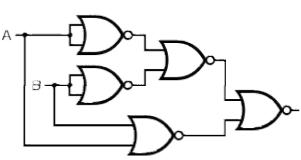

### NANDGATE:-

a) InverterfromNANDgate

Input =A Output Q=A

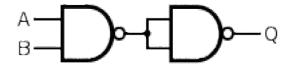

b) ANDgatefromNANDgate

InputsareAandB Output Q=A.B

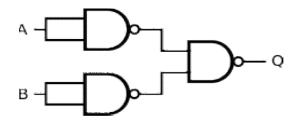

### c) **ORgatefromNANDgate**

InputsareAandB Output Q=A+B

d) NORgatefromNANDgate

Inputsare<u>Aand</u>B Output **Q=A+B**

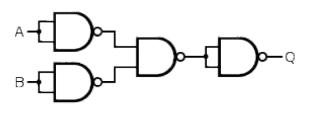

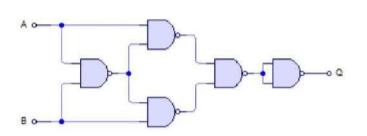

### e) <u>EX-ORgatefromNANDgate</u>

InputsareAandB Output Q=AB +AB

### f) <u>EX-NORgateFromNANDgate</u>

### NORGATE:-

a) InverterfromNORgate Input =A Output Q=A

b) <u>ANDgatefromNORgateIn</u> put s are A and BOutput Q = A.B

#### c) **ORgatefromNORgate**

InputsareAandB Output Q=A+B

#### d) NANDgatefromNORgate

InputsareAandB Output Q=A.B

e) <u>EX-ORgatefromNORgate</u>

InputsareAandB Output Q=AB +AB

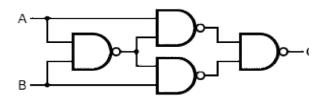

### f) <u>EX-NORgateFromNORgate</u>

Inputs are A and B\_ Output Q=AB +A B

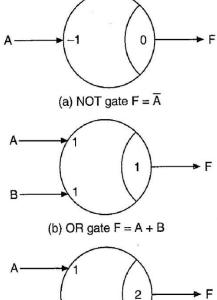

# THRESHOLDLOGIC:-

### INTRODUCTION:-

- <sup>1</sup> Thethresholdelement, also called the thresholdgate (T-gate) is a much more powerful device than any of the conventional logic gates such as NAND, NOR and others.

- Complex, largeBoolean functions can be realized using much fewer threshold gates.

- Frequentlyasingle threshold gate can realize averycomplexfunction whichotherwise mightrequire a large number of conventional gates.

- <sup>1</sup> T-gate offersincomparablyeconomicalrealization; it hasnotfoundextensiveuse with the digital system designers mainly because of the following limitations.

- 1. Itisverysensitivetoparametervariations.

- 2. Itisdifficulttofabricate itinICform.

3. Thespeedofswitchingofthresholdelementsinmuchlowerthanthatofconventionalgates.

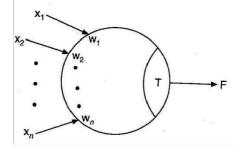

### THETHRESHOLDELEMENTS:-

- A threshold element or gate has 'n' binary inputs x<sub>1</sub>, x<sub>2</sub>, ...., x<sub>n</sub>; and a single binary output F. But in addition to those, it has two more parameters.

- ItsparametersareathresholdTandweightsw<sub>1</sub>,w<sub>2</sub>,...,w<sub>n</sub>.Theweightsw<sub>1</sub>,w<sub>2</sub>,...,w<sub>n</sub>areassociated with the input variables x<sub>1</sub>, x<sub>2</sub>, ...,x<sub>n</sub>.

- 1 The value of the threshold (T) and weights may be real, positive or negative number. The

- symbol of the threshold element is shown in fig.(a).

- Itisrepresentedbyacircle partitioned intotwoparts,onepart representstheweightsandother represents T.

- I Itisdefinedas

$\begin{array}{c} n\\ F(x_1,x_2,\ldots,x_n)=1 \text{ if and only if } \sum_{i=1}^{n} w_i x_i \geq T\\ i=1\\ \text{otherwise}\\ F(x_1,x_2,\ldots,x_n)=0 \end{array}$

n

i=1

$\Box$  The sumand productoperationarenormalarithmetic operations and the sum  $\sum w_i x_i {\geq} T$

iscalled the weighted sum of the elementor gate.

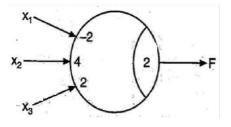

Example:-

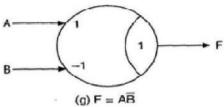

ObtaintheminimalBooleanexpressionfromthethresholdgateshowninfigure.

#### Solution:-

The threshold gate with three inputs  $x_1$ ,  $x_2$ ,  $x_3$  with weights  $-2(w_1)$ ,  $4(w_2)$  and  $2(w_3)$  respectively. The value of threshold is 2(T). The table shown is the weighted sums and outputs for all input combinations. For this threshold gate, the weighted sum is

$$w = w_1 x_1 + w_2 x_2 + w_3 x_3$$

=(-2)x\_1+(4)x\_2+(2)x\_3

=-2x\_1+4x\_2+2x\_3

TheoutputFislogic1forw≥2anditis logic0forw<2

| InputVariables |            | es         | WeightedSum               | Output |

|----------------|------------|------------|---------------------------|--------|

| <b>X</b> 1     | <b>X</b> 2 | <b>X</b> 3 | $w = -2x_1 + 4x_2 + 2x_3$ | F      |

| 0              | 0          | 0          | 0                         | 0      |

| 0              | 0          | 1          | 2                         | 1      |

| 0              | 1          | 0          | 4                         | 1      |

| 0              | 1          | 1          | 6                         | 1      |

| 1              | 0          | 0          | -2                        | 0      |

| 1              | 0          | 1          | 0                         | 0      |

| 1              | 1          | 0          | 2                         | 1      |

| 1              | 1          | 1          | 4                         | 1      |

From theinput-outputrelationisgiveninthetable,theBooleanexpressionfor theoutputis

TheK-mapforF is

### UNIVERSALITYOFAT-GATE:-

- A single T-gate can realize a large numberoffunctions by merely changing either the weights or the threshold or both, which can be done by altering the value of the corresponding resistors.

- Sinceathresholdgate canrealize universalgates, i.e., NANDgatesand NORgates, athresholdgate is also a universal gate.

- SinglethresholdgatecannotrealizebyasingleT-gate

- RealizationoflogicgatesusingT-gatesisshownin thebelowfigure.

(c) AND gate F = AB

(d)  $F = \overline{A} + \overline{B} = \overline{AB}$

(e)  $F = A \cdot B = \overline{A + B}$

| Input | Weighted sum | Output |

|-------|--------------|--------|

| A     | W = -A       | F      |

| 0     | 0            | 1      |

| 1     | -1           | 0      |

| Inputs |   | Weighted sum | Output   |

|--------|---|--------------|----------|

| A      | В | w = A + B    | F        |

| 0      | 0 | 0            | 0        |

| 0      | 1 | 1            | 1        |

| 1      | 0 | 1            | <u> </u> |

| 1      | 1 | 2            | 1        |

| Inputs |   | Weighted sum | Output |

|--------|---|--------------|--------|

| A      | В | w = A + B    | F      |

| 0      | 0 | 0            | 0      |

| 0      | 1 | 1            | 0      |

| 1      | 0 | 1            | 0      |

| 1      | 1 | 2            | 1      |

| Inputs |   | Weighted sum | Output |  |

|--------|---|--------------|--------|--|

| A B    |   | w = -A - B   |        |  |

| 0      | 0 | 0            | 1      |  |

| 0      | 1 | -1           | 1      |  |

| 1      | 0 | -1           | 1      |  |

| 1      | 1 | -2           | 0      |  |

| Inpute<br>A B |   | Weighted sum | Output |

|---------------|---|--------------|--------|

|               |   | w = -A - B   | F      |

| 0             | 0 | 0            | 1      |

| 0             | 1 | -1           | 0      |

| 1             | 0 | -1           | 0      |

| 1             | 1 | -2           | 0      |

| Inputs<br>A B |   | Weighted sum | Output |

|---------------|---|--------------|--------|

|               |   | w = -A + B   | F      |

| 0             | 0 | 0            | 0      |

| õ             | 1 | 1            | 1      |

| 1             | 0 | -1           | 0      |

| 1             | 1 | 0            | 0      |

| Inputs |   | Weighted sum | Output |  |

|--------|---|--------------|--------|--|

| A      | в | w = A - B    | F      |  |

| 0      | 0 | 0            | 0      |  |

| 0      | 1 | -1           | 0      |  |

| 1      | 0 | 1            | 1      |  |

| 1      | 1 | 0            | 0      |  |

# **BOOLEAN ALGEBRA**

# **INTRODUCTION:-**

- Switchingcircuitsarealsocalledlogiccircuits,gatescircuitsanddigitalcircuits.

- Switching algebra is also called Boolean algebra.

- Booleanalgebra isasystemof mathematicallogic. It isan algebraicsystemconsisting of the set of elements (0,1), two binary operators called OR and AND and unary operator called NOT.

- I Itisthebasicmathematicaltoolintheanalysisand synthesisof switching circuits. It is a

- way to express logic functions algebraically.

- Anycomplex logic canbeexpressedbyaBooleanfunction.

- I TheBooleanalgebraisgovernedbycertainwelldevelopedrulesandlaws.

# AXIOMSANDLAWSOFBOOLEANALGEBRA:-

Axioms or postulates of Boolean algebra are set of logical expressions that are accepted without proof and upon which we can build a set of useful theorems. Actually, axioms are nothing more than the definitions of the three basic logic operations AND, OR and INVERTER. Each axiom can be interpreted as the outcome of an operation performed by a logic gate.

| ANDoperation    | OR operation | NOToperation |

|-----------------|--------------|--------------|

| Axiom 1: 0. 0=0 | Axiom5:0+0=0 | Axiom 9:1=0  |

| Axiom 2:0.1=0   | Axiom6:0+1=1 | Axiom10:0=1  |

| Axiom 3:1.0=0   | Axiom7:1+0=1 |              |

| Axiom 2:1.1=1   | Axiom8:1+1=1 |              |

### 1. ComplementationLaws:-

Theterm complementsimply means invert, i.e.to changes0s to 1s and1sto0s.Thefive lawsof complementation are as follows:

Law1: $0=\overline{1}$ Law2:1=0 \_ Law3:ifA =0,thenA=1 Law4:ifA=1,thenA=  $\overline{0}$ Law5:  $\overline{A}=0$ (doublecomplementationlaw) 2. ORLaws:-ThefourORlawsareasfollows

Law 1: A + 0 = 0(Null law) Law2: A + 1 = 1(Identitylaw) Law 3: A + A = ALaw4: A + A = 1

### 3. ANDLaws:-

The four AND laws are as follows Law 1:  $A \cdot 0 = 0$ (Null law) Law2: $A \cdot 1 = 1$ (Identitylaw) Law 3:  $A \cdot A = A$ Law4:  $A \cdot A = 0$

### 4. CommutativeLaws:-

CommutativelawsallowchangeinpositionofANDorORvariables.Therearetwocommutativelaws.

=

=

Law1: A +B =B+ A Proof

| Α | В | A+B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

| В | Α | B+A |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

Law2: A .B =B.A

Proof

| Α | В | A.B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

| В | Α | B.A |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

Thislawcanbeextendedtoanynumberof variables. Forexample A.B. C=B.C. A =C. A.B=B. A.C

#### 5. AssociativeLaws:-

The associative laws allow grouping of variables. There are 2 associative laws. Law1: (A+B)+C=A+(B+C)

#### Proof

| Α | В | С | A+B | (A+B)+C |

|---|---|---|-----|---------|

| 0 | 0 | 0 | 0   | 0       |

| 0 | 0 | 1 | 0   | 1       |

| 0 | 1 | 0 | 1   | 1       |

| 0 | 1 | 1 | 1   | 1       |

| 1 | 0 | 0 | 1   | 1       |

| 1 | 0 | 1 | 1   | 1       |

| 1 | 1 | 0 | 1   | 1       |

| 1 | 1 | 1 | 1   | 1       |

=

| Α | В | С | B+C | A+(B+C) |

|---|---|---|-----|---------|

| 0 | 0 | 0 | 0   | 0       |

| 0 | 0 | 1 | 1   | 1       |

| 0 | 1 | 0 | 1   | 1       |

| 0 | 1 | 1 | 1   | 1       |

| 1 | 0 | 0 | 0   | 1       |

| 1 | 0 | 1 | 1   | 1       |

| 1 | 1 | 0 | 1   | 1       |

| 1 | 1 | 1 | 1   | 1       |

| Α | В | С | AB | (AB)C |

|---|---|---|----|-------|

| 0 | 0 | 0 | 0  | 0     |

| 0 | 0 | 1 | 0  | 0     |

| 0 | 1 | 0 | 0  | 0     |

| 0 | 1 | 1 | 0  | 0     |

| 1 | 0 | 0 | 0  | 0     |

| 1 | 0 | 1 | 0  | 0     |

| 1 | 1 | 0 | 1  | 0     |

| 1 | 1 | 1 | 1  | 1     |

| Α | В | С | B.C | A(B.C) |

|---|---|---|-----|--------|

| 0 | 0 | 0 | 0   | 0      |

| 0 | 0 | 1 | 0   | 0      |

| 0 | 1 | 0 | 0   | 0      |

| 0 | 1 | 1 | 1   | 0      |

| 1 | 0 | 0 | 0   | 0      |

| 1 | 0 | 1 | 0   | 0      |

| 1 | 1 | 0 | 0   | 0      |

| 1 | 1 | 1 | 1   | 1      |

Thislawcanbe extended to any number of variables. For example

A(BCD) = (ABC)D = (AB) (CD)

### 6. DistributiveLaws:-

$\label{eq:linear} The distributive laws allow factoring or multiplying out of expressions. There are two distributive laws. \\ Law1: A(B+C) = AB + AC$

=

Proof

| Α | В | С | B+C | A(B+C) |  |

|---|---|---|-----|--------|--|

| 0 | 0 | 0 | 0   | 0      |  |

| 0 | 0 | 1 | 1   | 0      |  |

| 0 | 1 | 0 | 1   | 0      |  |

| 0 | 1 | 1 | 1   | 0      |  |

| 1 | 0 | 0 | 0   | 0      |  |

| 1 | 0 | 1 | 1   | 1      |  |

| 1 | 1 | 0 | 1   | 1      |  |

| 1 | 1 | 1 | 1   | 1      |  |

=

| Α | В | С | AB | AC | A+(B+C) |

|---|---|---|----|----|---------|

| 0 | 0 | 0 | 0  | 0  | 0       |

| 0 | 0 | 1 | 0  | 0  | 0       |

| 0 | 1 | 0 | 0  | 0  | 0       |

| 0 | 1 | 1 | 0  | 0  | 0       |

| 1 | 0 | 0 | 0  | 0  | 0       |

| 1 | 0 | 1 | 0  | 1  | 1       |

| 1 | 1 | 0 | 1  | 0  | 1       |

| 1 | 1 | 1 | 1  | 1  | 1       |

Law2: A +BC=(A+B)(A+C) Proof RHS=(A+B)(A+C) =AA + AC+ BA +BC =A+AC+AB+BC =A(1+C+B)+BC =A. 1+BC (1+C+B=1+B=1) =A+BC =LHS 7. RedundantLiteralRule(RLR):-Law 1: A +  $\overline{AB}$  = A + B Proof

$$A+A\overline{B} = (A+A)(\overline{A} + B)$$

$$= 1. (A+B)$$

$$= A+B$$

Law2:A(

$$\overline{A+B}$$

)=AB A(A +

Proof

$\begin{array}{c} B) \stackrel{-}{=} AA + AB \\ = 0 + AB \\ = AB \end{array}$

#### 8. IdempotenceLaws:-

Idempotencemeanssamevalue.

Law1:A.A=A

#### Proof

If A = 0, then A.A = 0.0 = 0 = A If A=1, thenA.A = 1.1 = 1 = AThislawstatesthatANDofavariablewithitselfisequaltothatvariableonly.

**Law2:** A+A = A

### Proof

If A=0, then A + A = 0 + 0 = 0 = A If A=1, then A + A = 1 + 1 = 1 = A This laws tates that OR of avariable with itself is equal to that variable only.

### 9. AbsorptionLaws:-

Therearetwolaws:

**Law1:** A +A •B= A

### Proof

$A+A\cdot B=A(1+B)=A\cdot 1=A$

| Α | В | AB | A+AB |

|---|---|----|------|

| 0 | 0 | 0  | 0    |

| 0 | 1 | 0  | 0    |

| 1 | 0 | 0  | 1    |

| 1 | 1 | 1  | 1    |

**Law2:** A(A+ B)= A

Proof

$A(A + B) = A \cdot A + A \cdot B = A + AB = A(1 + B) = A \cdot 1 = A$

| Α | В | A+B | A(A+B) |

|---|---|-----|--------|

| 0 | 0 | 0   | 0      |

| 0 | 1 | 1   | 0      |

| 1 | 0 | 1   | 1      |

| 1 | 1 | 1   | 1      |

```

10. ConsensusTheorem(IncludedFactorTheorem):-

Theorem 1:

AB+AC+BC=AB +AC

Proof

LHS=AB+AC+BC

=AB+AC+BC(A+A)

=AB +AC+BCA +BCA

=AB(1+ <u>C</u>)+AC(1+B)

=AB(1)+AC(1)

=AB + AC

=RHS

Theorem2:

(A+B)(A+C)(B+C) = (A+B)(A+C)^{-1}

Proof

LHS=(A+B)(A+\tilde{C})(B+C)

=(AA+AC+BA+BC)(B+C)

=(AC+BC+AB)(B+C)

=ABC+BC+AB+AC+BC+ABC

=AC+BC+AB

RHS = (A+B)(A+C)

=AA+AC+BC+AB

=AC+BC+AB

=LHS

11. TranspositionTheorem:-

Theorem:

AB+AC=(A+C)(A+B)

Proof

RHS=(A+C) (A+B)

=AA +CA +AB +CB

=0 +AC+AB+BC

=AC+AB+BC(A+A)

=AB+ <u>A</u>BC+ AC+ABC

```

### 12. DeMorgan'sTheorem:-

=AB + AC =LHS

DeMorgan's theorem represents two laws in Boolean algebra.

Law1:  $A + B = A \cdot B$

#### Proof

| Α | В | A+B | A+B |

|---|---|-----|-----|

| 0 | 0 | 0   | 1   |

| 0 | 1 | 1   | 0   |

| 1 | 0 | 1   | 0   |

| 1 | 1 | 1   | 0   |

|   | Α | В | Ā | В | AB |

|---|---|---|---|---|----|

|   | 0 | 0 | 1 | 1 | 1  |

| = | 0 | 1 | 1 | 0 | 0  |

|   | 1 | 0 | 0 | 1 | 0  |

|   | 1 | 1 | 0 | 0 | 0  |

Thislawstatesthat thecomplementof a sumof variablesisequalto theproductof theirindividual complem<u>ent</u>s.\_\_\_ Law2: A·B=A +B Proof

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | Α | В | A.B | A.B |   | Α | В | Ā | В |   |

|-------------------------------------------------------|---|---|-----|-----|---|---|---|---|---|---|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 0 | 0 | 0   | 1   |   | 0 | 0 | 1 | 1 |   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 0 | 1 | 0   | 1   | = | 0 | 1 | 1 | 0 |   |

|                                                       | 1 | 0 | 0   | 1   | - | 1 |   | 0 | 1 | ł |

|                                                       | 1 | 1 | 1   | 0   |   | - | U | 0 | I | _ |

This lawstates that thecomplementof aproductof variables is equal to the sum of their individual complements.

# **DUALITY:-**

The implication of the duality concept is that once a theorem or statement is proved, the dual also thus stand proved. This is called the principle of duality.

Dual

$[f(A,B,C,....,0,1,+,\cdot)]_{d}=f(A,B,C,...,1,0,\cdot,+)$ Relationsbetweencompl<u>ementanddual</u>  $f_{c}(A,B,C,....)=f(A,B,C,....)=f_{d}(A,B,C,...)$   $f_{d}(A,B,C,....)=f(A,B,C,....)=f_{c}(A,B,C,....)$

$The first relation states that the complement of a function f(A,B,C,...) can be obtained by complementing all the variables in the dual function f_d(A,B,C,....).$

$T \underline{hese condre} lation states that the dual can be obtained by complementing all the literals in f(A, B, C, ...).$

### DUALS:-

Givenexpression

| 1.  |                                                                       | ī=0                              |

|-----|-----------------------------------------------------------------------|----------------------------------|

| 2.  | 0.1=0                                                                 | 1+0=1                            |

| 3.  | 0.0=0                                                                 | 1+1=1                            |

| 4.  | 1.1=1                                                                 | 0+0=0                            |

| 5.  | A·0=0                                                                 | A+1=1                            |

| 6.  | A·1=A                                                                 | A+0=A                            |

| 7.  | A·A=A                                                                 | A+A=A                            |

| 8.  | A·A=0                                                                 | A+A=1                            |

| 9.  | A·B=B·A                                                               | A+B=B+A                          |

| 10. | $A \cdot (B \cdot C) = (A \cdot B) \cdot C$                           | A+ (B+C)=(A+B)+ C                |

| 11. | $A \cdot (B+C) = AB + AC$                                             | A+BC=(A+B)(A+C)                  |

| 12. | A(A+B)=A                                                              | A+AB=A                           |

| 13. | $\underline{A} \cdot (\underline{A} \cdot B) = \underline{A} \cdot B$ | <u>A+A</u> + <u>B=</u> A+B       |

| 14. | AB=A+B                                                                | A+B=A B                          |

| 15. | $(A+\underline{B})(A+C)(B+\underline{C})=(A+B)(A+C)$                  | AB+AC+ BC=AB+AC                  |

| 16. | A+BC=(A+B)(A+C)                                                       | A(B+C)=AB+AC                     |

| 17. | $(A+C)(\overline{A}+B)=AB+\overline{AC}$                              | AC+AB=(A+B)(A+C)                 |

| 18. | (A+B)(C+D)=AC+AD+BC+BD                                                | (AB+CD)=(A+C)(A+D)(B+C)(B+D)     |

| 19. | <u>A+B=AB+</u> AB+AB                                                  | $A\underline{B=(A+B)(A+B)}(A+B)$ |

| 20. | AB+A+AB=0                                                             | <del>A+B·</del> A·(A+B)=1        |

|     |                                                                       |                                  |

### SUM-OF-PRODUCTSFORM:-

- <sup>1</sup> This is also calleddisjunctive CanonicalForm(DCF)orExpandedSumof Products FormorCanonical Sum of Products Form.

- In thisform, the function is the sum of an umber of products terms where each product term contains all variables of the function either in complemented or uncomplemented form.

- I This can also be derived from the truth table by finding the sum of all the terms that corresponds to those combinations for which f'assumes the value 1.

Forexample

f(A, B,C)=AB+BC=<u>A</u>B (C+C)+BC(A +A) =A BC+ABC+ABC+ABC

- <sup>1</sup> Theproducttermwhichcontainsallthe variables of the functions either incomplemented or uncomplemented form is called a minterm.

- I Themintermisdenotedasmo,m1,m2....

- An 'n'variable function canhave 2nminterms.

- Anotherwayof representing the function in canonical SOP form is the showing the sum of minterms for which the function equals to 1.

For example

$f(A, B,C)=m_1+m_2+m_3+m_5$

or

```

f(A,B,C) =∑m (1,2,3,5)

```

where  $\sum$  m represents the sum of all the minterms whose decimal codes are given the parenthesis.

## PRODUCT-OF-SUMSFORM:-

- <sup>1</sup> Thisform isalso called as Conjunctive CanonicalForm (CCF) or Expanded Product- of Sums Form or CanonicalProductOfSumsForm.

- 1 Thisisbyconsidering the combinations for which f=0 Each

- term is a sum of all the variables.

- I The function  $f(A, B, C) = (A + \underline{B} + C \cdot C) + (\underline{A} + \underline{B} + C \cdot C)$

=(A+B+C)(A+B+C)(A+B+C)(A+B+C)

- <sup>1</sup> The sum term which contains each of the 'n' variables in eithercomplemented or uncomplemented form iscalledamaxterm.

- I Maxterm is represented s  $M_0$ ,  $M_1$ ,  $M_2$ , .....

Thus CCFof'f'maybewrittenas

$f(A,B,C)=M_0\cdot M_4\cdot M_6\cdot M_7$

or

Whererepresentedtheproductofallmaxterms.

### **CONVERSIONBETWEENCANONICALFORM:-**

The complement of a function expressed as the sum of minterms equals the sum of minterms missing from the original function.

Example:-

$f(A,B,C) = \sum m(0,2,4,6,7)$ Thishasa complementthatcanbeexpressedas

$f(A,B,C)=\sum m(1,3,5)=m_1+m_3+m_5$ If we complement f by De-Morgan's theorem we obtain 'f' in a form.

$f=(m_1+m_3+m_5)= m_1. m_3.m_5$

#### Example:-ExpandA(A+B)(A+B + C)to maxtermsandminterms. Solution:-

The maxterms  $M_6$  and  $M_7$  are missing in the POS form.

So, the SOP form will contain the minterms 6 and 7

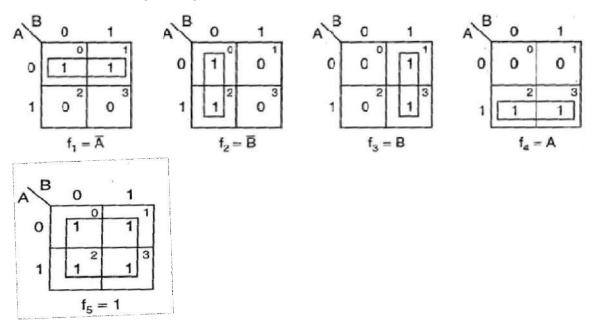

# KARNAUGHMAPORK-MAP:-

- <sup>I</sup> The K- mapis achart or agraph, composed of an arrangement of adjacent cells, each representing a particular combination of variables in sum or product form.

- <sup>1</sup> The K- map is systematic method of simplifying the Boolean expression.

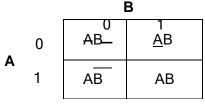

# **TWOVARIABLEK-MAP:-**

Atwovariableexpression canhave2<sup>2</sup>=4possible combinationsoftheinputvariablesAand B.

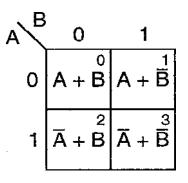

### MappingofSOPExpression:-

- The2 variableK-maphas2<sup>2</sup>=4squares.Thesesquaresarecalledcells.

- A '1' is placed in any square indicates that corresponding minterm is included in the output expression, and a 0 or no entry in any square indicates that the corresponding minterm does not appear in the expression for output.

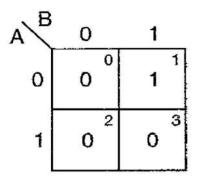

Example:-

Mapexpressionf=AB+AB

### Solution:-

Theexpressionmintermsis F

$= m_1 + m_2 = m(1, 2)$

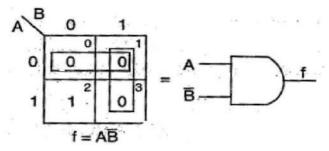

#### MinimizationofSOPExpression:-

To minimizea Booleanexpression given in the SOP form by using K- map, the adjacent squares having 1s, that is minterms adjacent to each other are combined to form larger squares to eliminate some variables. The possible minterm grouping in a two variable K-map are shown below

- Twominterms, which are adjacent to each other, can be combined to form a bigger square called 2– squareorapair. This eliminates one variable that is not common to both the minterms.

- Two 2-squares adjacent to each other can be combined to form a 4- square. A 4- square eliminates 2 variables. A 4-square is called a quad.

- <sup>1</sup> Consider only those variables which remain constant throughout the square, and ignore the variables which are varying. The non-complemented variable is the variable remaining constant as 1. The complemented variable is the variable remaining constant as a 0 and the variables are written as a product term.

### Example:-

Reduce the expression f=AB+AB+AB using mapping.

#### Solution:-

Expressedintermsof minterms, the given expression is f =

$$m_{0}+m_{1}+m_{3}=\sum m(0, 1, 3)$$

$$A = \frac{A}{0} = \frac{1}{1} = \frac{1}{1}$$

$$f = \overline{A} + B$$

$F = \overline{A} + B$

#### MappingofPOSExpression:-

Each sum term in the standard POS expression is called a Maxterm. A function in two variables (A,B) has 4 possible maxterms, A + B, A + B,  $\overline{A}$  + B and  $\overline{A}$  +  $\overline{B}$ . They are represented as M<sub>0</sub>, M<sub>1</sub>, M<sub>2</sub>and M<sub>3</sub>respectively.

ThemaxtermofatwovariableK-map

Example:-

Plottheexpressionf=(A+B)(A+B)(A+B)

Solution:-

Expressioninterms of maxterms is  $f=\Pi M(0,2,3)$

### MinimizationofPOSExpressions:-

In POS form the adjacent 0s are combined into large square as possible. If the squares having complemented variablethen the value remain constant as a 1 and the non-complemented variable if its value remains constant as a 0 along the entire square and then their sum term is written.

Thepossible maxtermsgroupinginatwo variableK-mapare shownbelow

## Example:-

# Reduce the expression f = (A+B)(A+B)(A+B) using mapping Solution:-

The given expression interms of maxterms is  $f=\Pi M(0,1,3)$

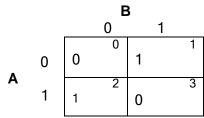

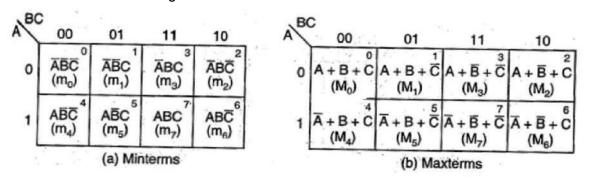

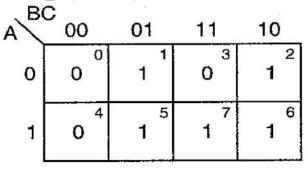

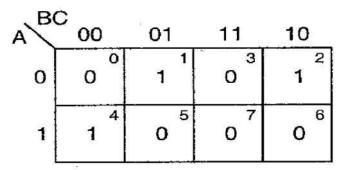

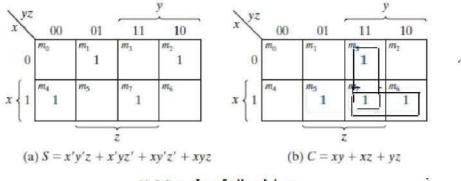

## THREEVARIABLEK-MAP:-

Afunctioninthreevariables(A,B,C)canbeexpressedinSOPandPOSformhavingeightpossible combination.A three variableK-maphave8 squaresorcellsandeachsquare onthemaprepresentsa minterm or maxterm is shown in the figure below.

## Example:-

## Maptheexpressionf= ABC+ABC+ABC+ABC

## Solution:-

SointheSOP form the expression is  $f=\sum m(1,5,2,6,7)$

Example:-

Mapthe expressionf= (A+ B+ C)(A+ B+C)(A+ B+ C)(A+ B+ C)(A+ B+ C)

## Solution:-

Sointhe POS form the expression is  $f=\Pi M(0,5,7,3,6)$

## MinimizationofSOPandPOSExpressions:-

ForreducingtheBooleanexpressionsinSOP(POS)formthefollowingstepsaregivenbelow

- I DrawtheK-mapandplace1s(0s)corresponding totheminterms(maxterms)ofthe SOP(POS)expression.

- In themap1s(0s) which are not adjacent to any other 1(0) are the isolated minterms (maxterms). They are to be read as they are because they cannot be combined even into a2-square.

- Forthose1s(0s)whichareadjacenttoonlyoneother1(0)makethempairs (2squares).

- For quads (4- squares)and octet (8squares)of adjacent1s (0s) evenif theycontain some1s (0s) which have already been combined. They must geometrically form a square or a rectangle.

- Forany1s(0s)that have notbeen combined yet then combine them into biggers quares if possible. Form the

- I minimal expression by summing (multiplying) the product (sum) terms of all the groups.

SomeofthepossiblecombinationsofmintermsinSOPform

These possiblecombinationsarealsoforPOSbut1sarereplacedby0s.

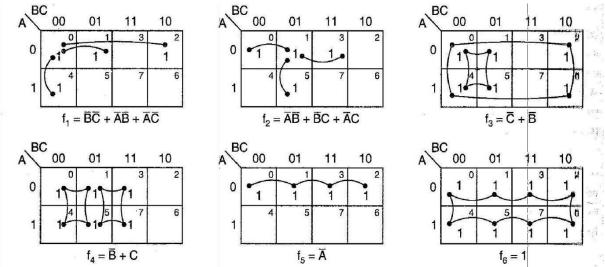

# FOURVARIABLEK-MAP:-

A four variable (A, B, C, D) expression can have  $2^4 = 16$  possible combinations of input variables. A four variable K-map has  $2^4 = 16$  squares or cells and each square on the map represents either a minterm or a maxterm as shown in thefigure below. Thebinarynumber designations of the rows and columnsare in the gray code. The binary numbers along the top of the map indicate the conditions of C and D along any column and binary numbers along left side indicate the conditions of A and B along any row. The numbers in the top right corners of the squares indicate the minterm or maxterm designations.

## SOPFORM

| AB | D 00                       | 01                             | 11                               | 10                             |  |  |  |

|----|----------------------------|--------------------------------|----------------------------------|--------------------------------|--|--|--|

| 00 |                            | 1<br>ABCD<br>(m <sub>1</sub> ) | 3<br>ABCD<br>(m <sub>3</sub> )   | 2<br>ABCD<br>(m <sub>2</sub> ) |  |  |  |

| 01 | ABCD<br>(m₄)               |                                | 7<br>ABCD<br>(m <sub>7</sub> )   | ABCD<br>(m <sub>6</sub> )      |  |  |  |

| 11 | ABCD<br>(m <sub>12</sub> ) | ABCD<br>(m <sub>13</sub> )     | 15<br>ABCD<br>(m <sub>15</sub> ) | ABCD<br>(m <sub>14</sub> )     |  |  |  |

| 10 |                            | 9<br>ABCD<br>(m <sub>9</sub> ) | ABCD<br>(m <sub>11</sub> )       | ABCD<br>(m <sub>10</sub> )     |  |  |  |

| -  | SOP form                   |                                |                                  |                                |  |  |  |

## POSFORM

|    | D 00                                                                       | 01                                                                        | 11                                                                     | 10                                                                     |

|----|----------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------|

| 00 | A + B + C + D<br>(M <sub>0</sub> )                                         | $A + B + C + \overline{D}$ (M <sub>1</sub> )                              | $A + B + \overline{C} + \overline{D}$ (M <sub>3</sub> )                | $A + B + \overline{C} + D$ $(M_2)$                                     |

| 01 | $ \begin{array}{c}     A + \overline{B} + C + D \\     (M_4) \end{array} $ | $\begin{array}{c} A+\overline{B}+C+\overline{D}\\ (M_5) \end{array}^5$    | $A + \overline{B} + \overline{C} + \overline{D}$ (M <sub>7</sub> )     | $\begin{array}{c} A+\overline{B}+\overline{C}+D\\ (M_6) \end{array}^6$ |

| 11 | $\overline{A} + \overline{B} + C + D$ $(M_{12})$ <sup>12</sup>             | $\overline{A} + \overline{B} + C + \overline{D}$ $(M_{13})$ <sup>13</sup> | $\overline{A} + \overline{B} + \overline{C} + \overline{D}$ $(M_{15})$ | $\overline{A} + \overline{B} + \overline{C} + D$ $(M_{14})$            |

| 10 | A + B + C + D<br>(M <sub>8</sub> )                                         | $\overline{A} + B + C + \overline{D}$<br>(M <sub>9</sub> )                | $\overline{A} + B + \overline{C} + \overline{D}$ $(M_{11})$            | $\overline{A} + B + \overline{C} + D$ $(M_{10})$                       |

|    |                                                                            |                                                                           |                                                                        |                                                                        |

## MinimizationofSOPandPOSExpressions:-

$\label{eq:powerserv} For reducing the Boolean expressions in SOP (POS) form the following steps are given below$

- I Draw the K-mapandplace1s(0s) corresponding to theminterms (maxterms) of the SOP (POS) expression.

- In themap1s(0s) which are not adjacent to any other 1(0) are the isolated minterms (maxterms). They are to be read as they are because they cannot be combined even into a2-square.

- For those 1s (0s) which are adjacent to only one other 1(0) make them pairs (2squares).

- For quads (4- squares)and octet (8 squares)of adjacent 1s (0s) even if they contain some 1s (0s) which have already been combined. They must geometrically form a square or a rectangle.

- I Forany1s(0s)that have notbeen combined yetthen combine them into biggers quares if possible. Form the

- I minimal expression by summing (multiplying) the product (sum) terms of all the groups.

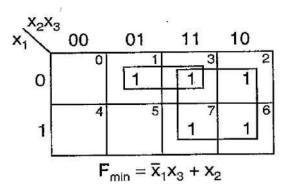

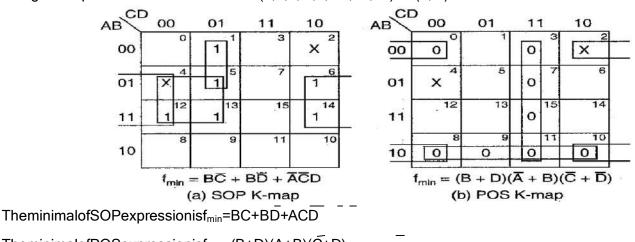

Example:-

# Reduce using mapping the expression f= $\sum m(0, 1, 2, 3, 5, 7, 8, 9, 10, 12, 13)$

## Solution:-

The given expression in POS form is  $f=\Pi M(4, 6, 11, 14, 15)$  and in SOP form  $f=\sum m(0, 1, 2, 3, 5, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7, 8, 9, 7$

10, 12, 13)

TheminimalSOPexpressionisfmin=BD+AC+AD

The minimal POS expression is  $f_{min} = (A+B+D) (A+C+D) (\overline{A}+B+C)$

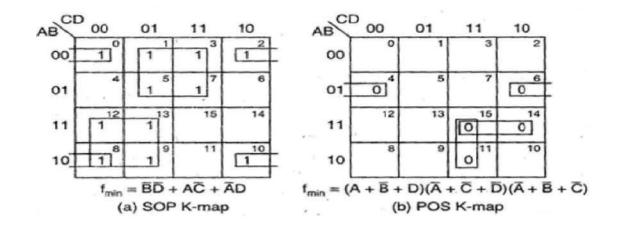

# **DON'TCARECOMBINATIONS:-**

The combinationsforwhichthe valuesof theexpression arenot specified are called don'tcare combinations or optional combinations and such expression stand incompletely specified. The output is a don't care for these invalid combinations. The don't care terms are denoted by d or X. During the process of designing using SOP maps, each don't care is treated as 1 to reduce the map otherwise it is treated as 0 and left alone. During the process of designingusing POS maps, each don't care is treated as0 to reduce the map otherwise it is treated as 1 and left alone.

A standard SOP expression with don't cares can be converted into standard POS form by keeping the don't cares as they are, and the missing minterms of the SOP form are written as the maxterms of the POS form. Similarly, to convert a standard POS expression with don't cares can be converted into standard SOP form by keeping the don't cares as they are, and the missing maxterms of the POS form are written as the minterms of the SOP form.

## Example:-

## Reduce the expression $f=\sum m(1, 5, 6, 12, 13, 14)+d(2, 4)$ using K-map.

## Solution:-

The given expression in SOP form is  $f=\sum m (1,5,6,12,13,14)+d(2,4)$

The givenexpression in POS form is f= ΠM(0,3,7, 8,9, 10,11,15) + d(2, 4)

The minimal of POS expression is  $f_{min} = (B+D)(A+B)(C+D)$  -

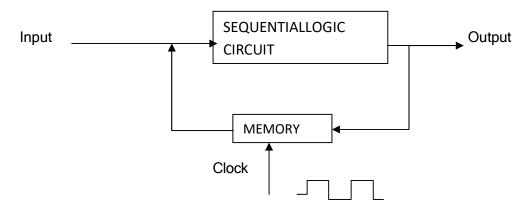

# <u>SEQUENTIALLOGICCIRCUIT</u>

## SEQUENTIALCIRCUIT:-

It is a circuit whose output depends upon the present input, previous output and the sequence inwhich the inputs are applied.

## HOW THESEQUENTIALCIRCUITISDIFFERENTFROMCOMBINATIONALCIRCUIT?:-

- In combinational circuit output depends upon present input at any instant of time and do notusememory. Hence previous input does not have any effect on the circuit. But sequential circuit hasmemory and depends upon present input and previous output.

- I Sequential circuits are slower than combinational circuits and these sequential circuits are harder to design.

[BlockdiagramofSequentialLogicCircuit]

<sup>1</sup> Thedata storedby thememoryelementat anygiven instantof time iscalled the present state of sequential circuit.

## TYPES:-

Sequentiallogiccircuits(SLC)areclassifiedas

- (i) SynchronousSLC

- (ii) AsynchronousSLC

- <sup>1</sup> TheSLCthatare controlled byclockarecalled synchronousSLCand those whicharenot controlled by a clock are asynchronous SLC.

- <sup>I</sup> Clock:- A recurring pulse is called a clock.

## FLIP-FLOPANDLATCH:-

- Aflip-floporlatchisacircuit thathastwostablestatesandcanbeused tostoreinformation.

- Aflip-flop is a binary storage device capable of storing one bit of information. In a stable state, the output of a flip-flop is either 0 or 1.

- Latchisanon-clockedflip-flopanditisthebuilding blockfortheflip-flop.

- A storage element in digital circuit can maintain abinary state indefinitely until directed by an input signal to switch state.

- Storageelement that operate with signal level are called latches and those operate with clock transition are called as flip-flops.

- <sup>1</sup> The circuit canbemade to change stateby signals applied to one or more control inputs and will have one or two outputs.

- Aflip-flopiscalled so because its output eitherflips or flops meaning to switch back and forth.

- Aflip-flop is also called a bi-stable multi-vibratorasit has two stable states. The input signals which command the flip-flop to change state are called excitations.

- I Flip-flopsarestorage devicesandcan store1or0.

- Flip-flopsusing the clocksignalare called clocked flip-flops. Control signals are effective only if they are applied in synchronization with the clock signal.

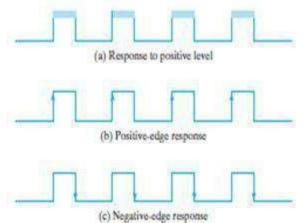

- Clock-signalsmaybepositive-edgetriggeredornegative-edgetriggered.

- Positive-edgetriggeredflip-flopsarethose in which statetransitions takeplaceonly atpositive-going edge of the clock pulse.

Negative-edge triggeredflip-flopsarethose in which state transition takeplaceonly atnegative-going edge of the clock pulse.

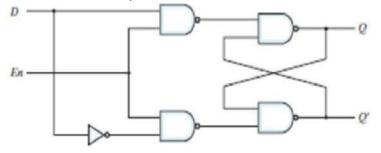

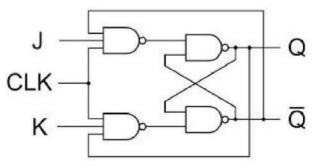

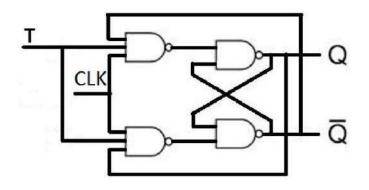

- I Some common type of flip-flops include

- a) SR(set-reset)F-F

- b) D(dataor delay)F-F

- c) T(toggle) F-Fand

- d) JKF-F

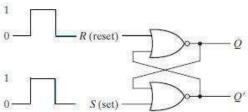

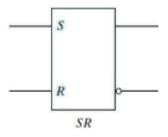

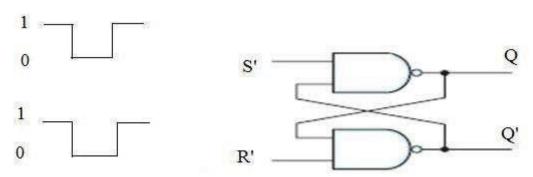

## SRlatch:-

- 1 TheSRlatch is a circuit with two cross-coupled NOR gates or two cross-coupled NAND gates.

- I It has twooutputs labeledQandQ'.TwoinputsaretherelabeledSforsetandRfoereset.

- Thelatchhastwousefulstates.WhenQ=0andQ'=1theconditioniscalledresetstateandwhenQ=1 andQ'=0theconditioniscalledsetstate.

- NormallyQand Q'are complementofeachother.

- The figure represents a SR latch with two cross-coupled NOR gates. The circuit has NOR gates and as we know ifany one of the input for a NOR gate is HIGH then its output will be LOW and if both the inputs are LOW then only the output will be HIGH.

- Under normal conditions, both inputs of the latch remain at 0 unless the state has to be changed. The application of a momentary 1 to the S input causes the latch to go to the set state. The S input must go back to 0 before any other changes take place, in order to avoid the occurrence of an undefined next state that results from the forbidden input condition.

- <sup>I</sup> The first condition (S= 1, R = 0) is the action that must be taken by input Stobring thecircuit to theset state. Removing the active input from S leaves thecircuit in the same state. After bothinputs returnto0, it is then possible to shift to the reset state by momentary applying a 1 to the R input. The 1 can then be removed from R, whereupon the circuit remains in the reset state. When both inputs S and R are equal to 0, the latch can be in either the set or the reset state, depending on which input was most recently a 1.

If a 1 is applied to both the S and R inputs of the latch, both outputs go to 0. This action produces an undefined next state, because the state that results from the input transitions depends on the order in which they return to 0. It also violates the requirement that outputs be the complement of each other. In normal operation, this condition is avoided by making sure that 1's are not applied to both inputs simultaneously.

| Inj | put | Output |    |                   | Comment            |            |

|-----|-----|--------|----|-------------------|--------------------|------------|

| S   | R   | Q      | Q' | Q <sub>Next</sub> | Q' <sub>Next</sub> | _          |

| 0   | 0   | 0      | 1  | 0                 | 1                  | Nochange   |

| 0   | 0   | 1      | 0  | 1                 | 0                  |            |

| 0   | 1   | 0      | 1  | 0                 | 1                  | Reset      |

| 0   | 1   | 1      | 0  | 0                 | 1                  |            |

| 1   | 0   | 0      | 1  | 1                 | 0                  | Set        |

| 1   | 0   | 1      | 0  | 1                 | 0                  |            |

| 1   | 1   | 0      | 1  | Х                 | Х                  | Prohibited |

| 1   | 1   | 1      | 0  | Х                 | Х                  | state      |

<sup>1</sup> Truth table for SR latch designed with NOR gatesis shownbelow.

SymbolforSRNORLatch

## RacingCondition:-

In caseof aSRIatch whenS=R=1inputis givenboth the output will try to become 0. This is called Racing condition.

## SRlatchusingNANDgate:-

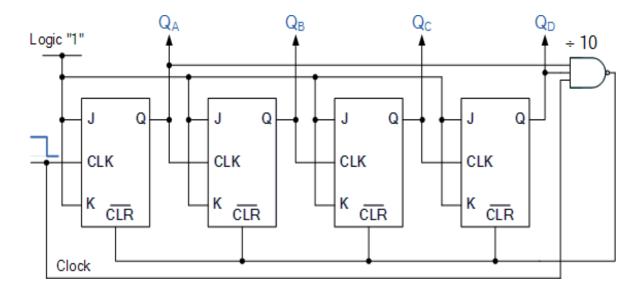

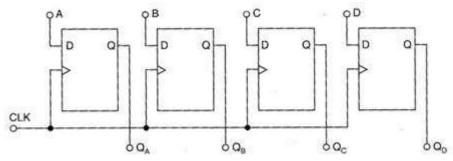

- I The below figure represents a SR latch with two cross-coupled NAND gates. The circuit hasNAND gates and as weknow ifany one oftheinput for aNAND gate LOWthen the output will beHIGH and if both the inputs are HIGH then only the output will be LOW.